1156гғ”гғігҒ®BGAгғ‘гғғгӮұгғјгӮёгҒӢгӮүй…Қз·ҡгӮ’еј•гҒҚеҮәгҒҷ

BGAгҒҜгҖҒй«ҳеҜҶеәҰе®ҹиЈ…гҒ®гҒҹгӮҒгҒ®LSIгғ‘гғғгӮұгғјгӮёгҒЁгҒ—гҒҰеёёз”ЁгҒ•гӮҢгҒҰгҒ„гҒҫгҒҷгҖӮй«ҳеҜҶеәҰеҢ–гҒёгҒ®иҰҒжұӮгҒҜз•ҷгҒҫгӮӢгҒ“гҒЁгҒҢгҒӘгҒҸгҖҒBGAгғ‘гғғгӮұгғјгӮёгҒ®з«Ҝеӯҗзҙ гҒҜеў—гҒҲгӮӢдёҖж–№гҒ§гҒҷгҖӮд»ҠгӮ„1000гғ”гғігҒҜеҪ“гҒҹгӮҠеүҚгҒ§гҖҒCPUгҒ§гҒҜ 5903гғ”гғігҒЁгҒ„гҒҶгӮӮгҒ®гҒҫгҒ§зҸҫгӮҢгҒҰгҒҚгҒҰгҒ„гҒҫгҒҷгҖӮгҒқгҒ“гҒ§е•ҸйЎҢгҒ«гҒӘгӮӢгҒ®гҒҢгҖҒBGAгҒҫгӮҸгӮҠгҒ®й…Қз·ҡгҒ§гҒҷгҖӮз«ҜеӯҗгҒҢ1,000жң¬гҒ«гӮӮгҒӘгӮӢгҒЁгҖҒй…Қз·ҡгӮ’еӨ–гҒ«еј•гҒҚеҮәгҒҷгҒ гҒ‘гҒ§дҪ•жҷӮй–“гӮӮгҒӢгҒӢгҒЈгҒҰгҒ—гҒҫгҒ„гҒҫгҒҷгҖӮ

гҒқгҒ“гҒ§еҪ№з«ӢгҒӨгҒ®гҒҢгҖҒгҖҢBGAгғ•гӮЎгғігӮўгӮҰгғҲгғ«гғјгғҶгӮЈгғігӮ°гҖҚж©ҹиғҪгҒ§гҒҷгҖӮгҒ“гҒ®ж©ҹиғҪгӮ’дҪҝгҒҶгҒЁгҖҒBGAз«ҜеӯҗгҒӢгӮүгҒ®й…Қз·ҡгҒ®еј•гҒҚеҮәгҒ—гҒҢгҒ»гӮ“гҒ®ж•°з§’гҒ§зөӮгӮҸгӮҠгҒҫгҒҷгҖӮ

гҒқгҒ“гҒ§гҖҒд»ҠеӣһгҒҜгҒ“гҒ®гҖҢBGAгғ•гӮЎгғігӮўгӮҰгғҲгҖҚж©ҹиғҪгӮ’и©ҰгҒ—гҖҒгҒқгҒ®жүӢй ҶгӮ’зҙ№д»ӢгҒ—гҒҫгҒҷгҖӮ

1156гғ”гғігҒ®BGAгҒӢгӮүй…Қз·ҡгӮ’еј•гҒҚеҮәгҒҷ

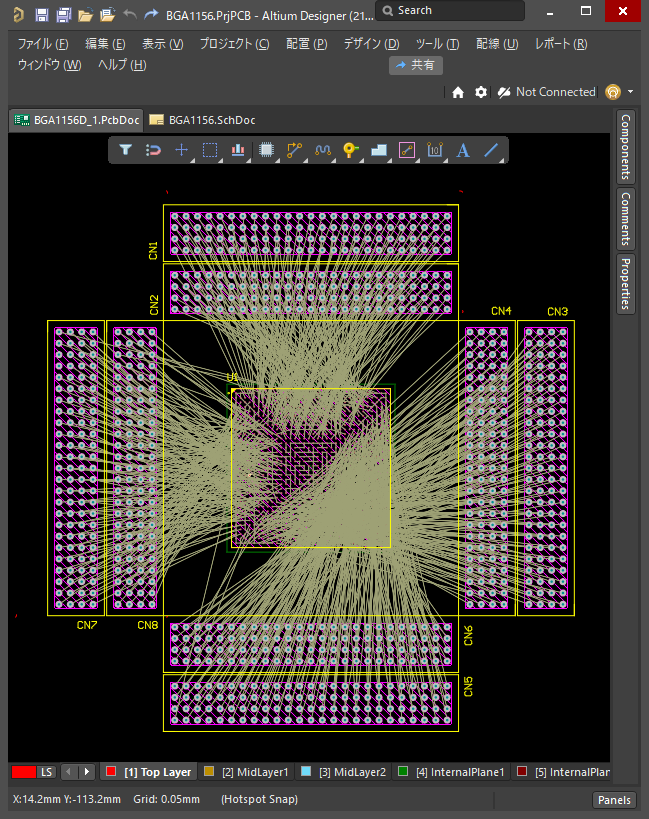

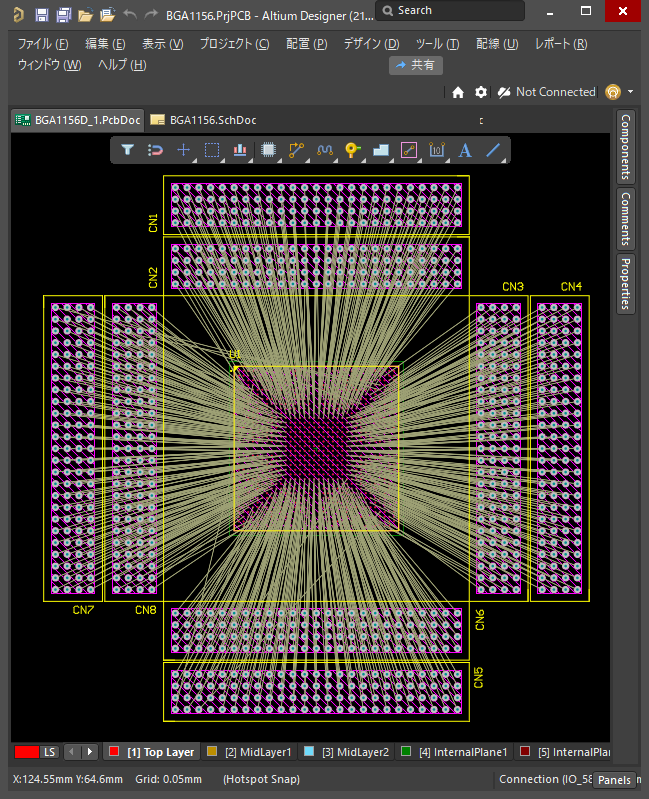

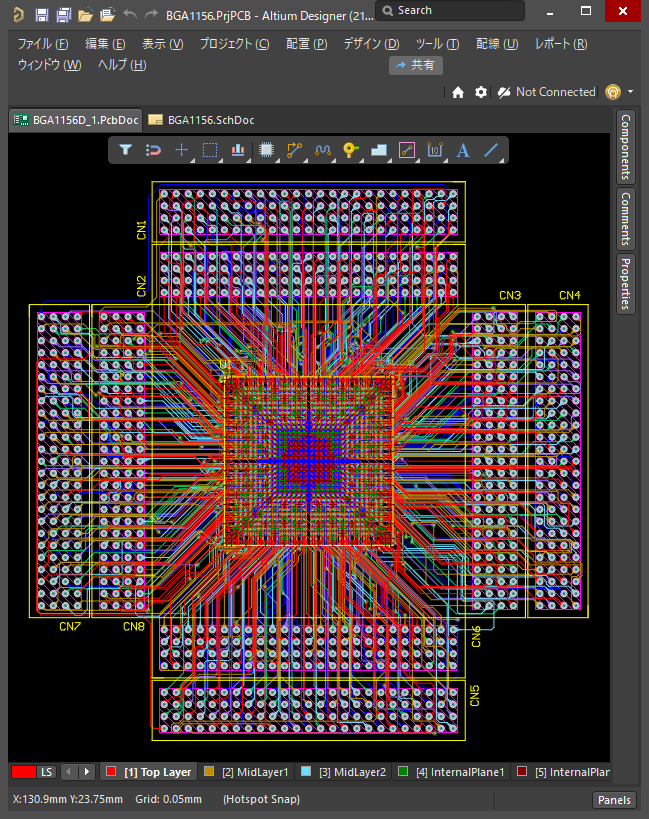

FPGAгҒ§гҒҜеӨҡгҒҸгҒ®IOз«ҜеӯҗгӮ’жҢҒгҒӨгӮӮгҒ®гҒҢеӨҡгҒҸгҖҒе°ҸеһӢеҢ–гҒ®гҒҹгӮҒгҒ«BGAгҒҢжЁҷжә–зҡ„гҒ«дҪҝз”ЁгҒ•гӮҢгҒҫгҒҷгҖӮгҒқгҒ“гҒ§гҖҒд»ҠеӣһгҒҜBGAгғҮгғҗгӮӨгӮ№гҒЁгҒ—гҒҰXilinx Spartan 3 - XC3S5000гӮ’еҸ–гӮҠдёҠгҒ’гҒҫгҒҷгҖӮгғ‘гғғгӮұгғјгӮёгҒҜгҖҒ1156гғ”гғігҒ§з«Ҝеӯҗгғ”гғғгғҒгҒҜ1.0mmгҒ§гҒҷгҖӮгҒқгҒ—гҒҰеј•гҒҚеҮәгҒ—гҒҹй…Қз·ҡгҒ®жҺҘз¶ҡе…ҲгҒЁгҒ—гҒҰгҖҒBGAгҒ®е‘ЁиҫәгҒ«8еҖӢгҒ®100гғ”гғігӮігғҚгӮҜгӮҝгӮ’й…ҚзҪ®гҒ—гҒҫгҒҷгҖӮ

гҒ“гҒ®FPGAгҒ§гҒҜгҖҒйӣ»жәҗз«ҜеӯҗгҒҢIOгғҗгғігӮҜгҒ”гҒЁгҒ«иЁӯгҒ‘гӮүгӮҢгҒҰгҒ„гҒҫгҒҷгҖӮгҒ•гӮүгҒ«гҖҒгҒ“гҒ®д»–гҒ«2зЁ®йЎһгҒ®йӣ»жәҗз«ҜеӯҗгҒҢгҒӮгӮҠгҒҫгҒҷгҒҢгҖҒд»ҠеӣһгҒҜIOз«ҜеӯҗгҒӢгӮүгҒ®й…Қз·ҡгҒ®еј•гҒҚеҮәгҒ—гҒ«з„ҰзӮ№гӮ’зөһгӮҠгҖҒгҒ“гӮҢгӮүгҒ®йӣ»жәҗз«ҜеӯҗгҒ®еҮҰзҗҶгҒҜз°Ўз•ҘеҢ–гҒ—гҒҰгҒ„гҒҫгҒҷгҖӮгҒҫгҒҹгҖҒгғҗгӮӨгғ‘гӮ№гӮігғігғҮгғігӮөгӮӮй…ҚзҪ®гҒ—гҒҰгҒ„гҒҫгҒӣгӮ“гҖӮ

BGAгғ‘гғғгӮұгғјгӮёгҒ®е‘ЁиҫәгҒ«гӮігғҚгӮҜгӮҝгӮ’й…ҚзҪ®гҒ—гҖҒIOз«ҜеӯҗгҒӢгӮүй…Қз·ҡгӮ’еј•гҒҚеҮәгҒ—гҒҰжҺҘз¶ҡгҒ—гҒҫгҒҷгҖӮ

гӮ№гӮҝгғғгӮҜгӮўгғғгғ—гҒЁгғҮгӮ¶гӮӨгғігғ«гғјгғ«гҒ®иЁӯе®ҡ

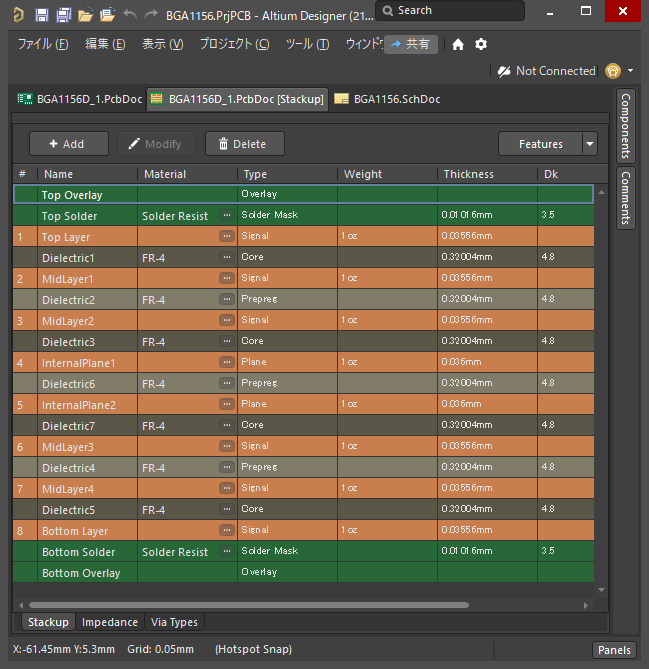

гҒҫгҒҡгҖҒй…Қз·ҡжҲҰз•ҘгҒ«еҹәгҒҘгҒҚгӮ№гӮҝгғғгӮҜгӮўгғғгғ—гҒЁгғҮгӮ¶гӮӨгғігғ«гғјгғ«гҒ®иЁӯе®ҡгӮ’иЎҢгҒ„гҒҫгҒҷгҖӮз«Ҝеӯҗж•°гҒ®еӨҡгҒ„BGAгҒ§гҒҜи©ҰиЎҢйҢҜиӘӨгӮ’з№°гӮҠиҝ”гҒҷдҪҷиЈ•гҒҜгҒӮгӮҠгҒҫгҒӣгӮ“гҒ®гҒ§гҖҒж®өеҸ–гӮҠиүҜгҒҸдҪңжҘӯгӮ’йҖІгӮҒгҒӘгҒҸгҒҰгҒҜгҒӘгӮҠгҒҫгҒӣгӮ“гҖӮгҒқгҒ®гҒҹгӮҒгҖҒеұӨж•°гҒ®иҰӢз©ҚгӮӮгӮҠгҒЁгғ«гғјгғ«иЁӯе®ҡгӮ’ж…ҺйҮҚгҒ«иЎҢгӮҸгҒӘгҒҸгҒҰгҒҜгҒӘгӮҠгҒҫгҒӣгӮ“гҖӮгҒқгҒ“гҒ§гҖҒд»ҠеӣһгҒҜеҚҒеҲҶгҒӘжӨңиЁҺгҒ®гҒҷгҒҲгҖҒй…Қз·ҡгҒ®з·ҡе№…гҒЁгӮҜгғӘгӮўгғ©гғігӮ№гӮ’0.15mmгҖҒеұӨж•°гӮ’8еұӨ(дҝЎеҸ·еұӨ6еұӨ+гғ—гғ¬гғјгғіеұӨ2еұӨ)гҒ«иЁӯе®ҡгҒ—гҒҫгҒ—гҒҹгҖӮгҒӘгҒҠгҖҒBGAгҒ®й…Қз·ҡжҲҰз•ҘгҒ«гҒӨгҒ„гҒҰгҒҜгҖҒBGAгғ‘гғғгӮұгғјгӮёгҒ®йҒёжҠһгҒЁй…Қз·ҡжҲҰз•ҘгҒ§и§ЈиӘ¬гҒ—гҒҰгҒ„гҒҫгҒҷгҒ®гҒ§еҸӮиҖғгҒ«гҒ—гҒҰгҒҸгҒ гҒ•гҒ„гҖӮ

PCBз”»йқўгҒӢгӮү [гғҮгӮ¶гӮӨгғі] - [гғ¬гӮӨгғӨж§ӢжҲҗ] гӮ’йҒёгҒігҖҒгӮ№гӮҝгғғгӮҜгӮўгғғгғ—гӮ’иЁӯе®ҡгҖӮдҝЎеҸ·еұӨ4еұӨгҒЁгҖҒгғ—гғ¬гғјгғіеұӨ2еұӨгҒ®гҖҒ8еұӨеҹәжқҝгҒ«иЁӯе®ҡгҒ—гҒҫгҒ—гҒҹгҖӮ

гғ”гғігӮ№гғҜгғғгғ—гӮ’иЎҢгҒҶ

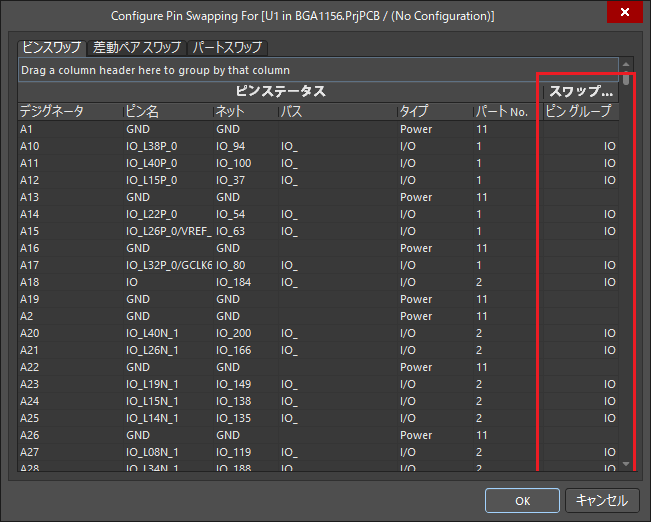

гӮөгғігғ—гғ«гғ¬гӮӨгӮўгӮҰгғҲгӮ’иҰӢгӮӢгҒЁгҖҒгғ©гғғгғ„гғҚгӮ№гғҲгҒ®дәӨе·®гҒҢзӣ®з«ӢгҒЎгҒҫгҒҷгҖӮгҒ“гҒ®дәӨе·®гӮ’жёӣгӮүгҒ—гҖҒгӮігғҚгӮҜгӮҝгҒЁгҒ®й–“гҒ®й…Қз·ҡгӮ’жңҖзҹӯеҢ–гҒҷгӮӢгҒҹгӮҒгҒ«гҖҒFPGAгҒ®I/Oз«ҜеӯҗгҒ®й…ҚеҲ—гӮ’еӨүжӣҙгҒ—гҒҫгҒҷгҖӮгҒ“гӮҢгҒ«гҒҜгҖҒгғ”гғігӮ№гғҜгғғгғ—ж©ҹиғҪгӮ’з”ЁгҒ„гҒҫгҒҷгҖӮд»ҠеӣһгҒҜгҖҒе…ЁгҒҰгҒ®IOз«ҜеӯҗгӮ’еҗҢгҒҳгӮ°гғ«гғјгғ—гҒ«иЁӯе®ҡгҒ—гҒҰгҖҒе…ҘгӮҢжӣҝгҒҲгӮ’иЁұеҸҜгҒҷгӮӢдәӢгҒ«гҒ—гҒҫгҒҷгҖӮ

PCBз”»йқўгҒӢгӮү [гғ„гғјгғ«] - [гғ”гғі/гӮІгғјгғҲгӮ№гғҜгғғгғ—] вҖ“ [иЁӯе®ҡ] гӮ’йҒёгҒігҖҒFPGAгғҮгғҗгӮӨгӮ№гҒ®гғ”гғігӮ№гғҜгғғгғ—жқЎд»¶гӮ’иЁӯе®ҡгҒ—гҒҫгҒҷгҖӮд»ҠеӣһгҒҜгҖҒе…ЁгҒҰгҒ®IOз«ҜеӯҗгӮ’еҗҢдёҖгӮ°гғ«гғјгғ—гҒ«иЁӯе®ҡгҒ—гҒҫгҒ—гҒҹгҒҢгҖҒе®ҹйҡӣгҒ®иЁӯиЁҲгҒ§гҒҜIOгғҗгғігӮҜгҒ®з”ЁйҖ”гҒ«еҗҲгӮҸгҒӣгҒҹиЁӯе®ҡгҒҢеҝ…иҰҒгҒ§гҒҷгҖӮ

иЁӯе®ҡеҫҢгҖҒгғ”гғігӮ№гғҜгғғгғ—е®ҹиЎҢгҒҷгӮӢгҒЁж•°з§’гҒ§еҮҰзҗҶгҒҢе®ҢдәҶгҒ—гҖҒгғ©гғғгғ„гғҚгӮ№гғҲгҒ®дәӨе·®гҒҢи§Јж¶ҲгҒ•гӮҢгҒҫгҒҷгҖӮ

В [гғ„гғјгғ«] - [гғ”гғі/гӮІгғјгғҲгӮ№гғҜгғғгғ—] - [иҮӘеӢ•гғҚгғғгғҲ/гғ”гғігҒ®жңҖйҒ©еҢ–] гӮ’йҒёгӮ“гҒ§гҖҒгғ”гғігӮ№гғҜгғғгғ—гӮ’е®ҹиЎҢгҒ—гҒҫгҒҷгҖӮж•°з§’гҒ§еҮҰзҗҶгҒҢе®ҢдәҶгҒ—гҖҒдәӨе·®гҒҢи§Јж¶ҲгҒ•гӮҢгҒҫгҒҷгҖӮ

гғ•гӮЎгғігӮўгӮҰгғҲгҒЁеј•гҒҚеҮәгҒ—й…Қз·ҡ

гғ•гӮЎгғігӮўгӮҰгғҲгғ»гғ«гғјгғҶгӮЈгғігӮ°ж©ҹиғҪгӮ’дҪҝгҒЈгҒҰBGAз«ҜеӯҗгҒӢгӮүгғ‘гғғгӮұгғјгӮёгҒ®еӨ–е‘ЁйғЁгҒ«й…Қз·ҡгӮ’еј•гҒҚеҮәгҒ—гҒҫгҒҷгҖӮгҒ“гҒ®еҮҰзҗҶгҒҜж•°з§’гҒ§зөӮгӮҸгӮҠгҒҫгҒҷгҖӮ

еј•гҒҚеҮәгҒ—гҒ«гҒҜгҖҒеҶ…еұӨгҒёгҒ®жҺҘз¶ҡгҒ®гҒҹгӮҒгҒ®гғ“гӮўгҒ®й…ҚзҪ®гҒЁгҖҒгғ“гӮўгҒӢгӮүгғ‘гғғгӮұгғјгӮёеӨ–е‘ЁгҒҫгҒ§гҒ®й…Қз·ҡгҒҢеҝ…иҰҒгҒ«гҒӘгӮҠгҒҫгҒҷгҖӮеӨ–еҒҙгҒ®2еҲ—гҒҜгғ“гӮўгҒҢз„ЎгҒҸгҒҰгӮӮеј•гҒҚеҮәгҒӣгҒҫгҒҷгҒҢгҖҒгҒқгӮҢгӮҲгӮҠеҶ…еҒҙгҒ®з«ҜеӯҗгҒ«гҒҜгғ“гӮўгҒҢеҝ…иҰҒгҒ§гҒҷгҖӮ

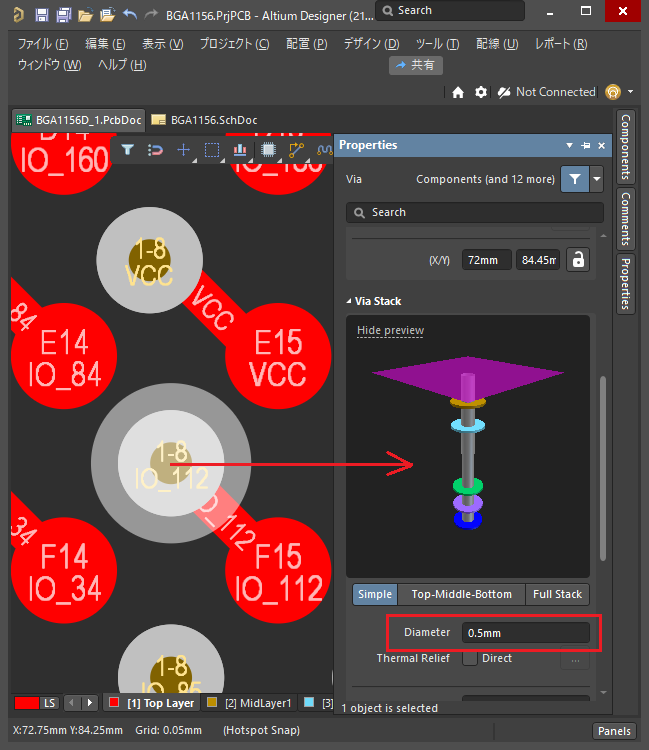

BGAз«ҜеӯҗгҒӢгӮүгҒ®й…Қз·ҡгҒ®еј•гҒҚеҮәгҒ—гҒ«гҒҜгҖҒе®ҹиЈ…йқўд»ҘеӨ–гҒ®еұӨгӮӮдҪҝз”ЁгҒ—гҒҫгҒҷгҒ®гҒ§гҖҒеұӨй–“гӮ’з№ӢгҒҗгҒҹгӮҒгҒ®гғ“гӮўгҒҢеҝ…иҰҒгҒ§гҒҷгҖӮгҒ“гӮҢгҒҜгҖҒгғ•гӮЎгғігӮўгӮҰгғҲж©ҹиғҪгҒ«гӮҲгҒЈгҒҰиҮӘеӢ•зҡ„гҒ«зҷәз”ҹгҒ•гҒӣгӮӢдәӢгҒҢгҒ§гҒҚгҒҫгҒҷгҖӮд»ҠеӣһгҒҜгҖҒгҒ“гӮҢгҒ«0.5mmгҒ®иІ«йҖҡгғ“гӮўгӮ’дҪҝз”ЁгҒ—гҒҫгҒҷгҖӮ

й…Қз·ҡгӮ’еј•гҒҚеҮәгҒҷ

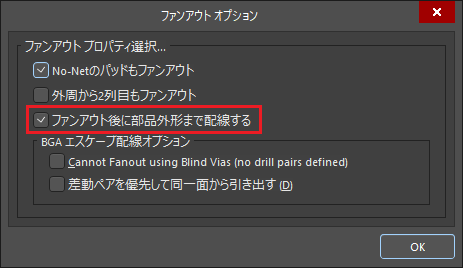

Altium DesignerгҒ§гҒҜгҖҒгғ•гӮЎгғігӮўгӮҰгғҲ(гғ“гӮўгҒ®зҷәз”ҹ)гҒЁеҗҢжҷӮгҒ«гғ‘гғғгӮұгғјгӮёгҒ®еӨ–е‘ЁйғЁгҒҫгҒ§гҒ®еј•гҒҚеҮәгҒ—гӮ’иҮӘеӢ•зҡ„гҒ«иЎҢгҒҶдәӢгҒҢгҒ§гҒҚгҒҫгҒҷгҖӮгҒ“гҒ®ж©ҹиғҪгҒҜгҖҒ[й…Қз·ҡ] - [гғ•гӮЎгғігӮўгӮҰгғҲ] - [гӮігғігғқгғјгғҚгғігғҲд»ҳйҡҸгғҚгғғгғҲ] гӮ’йҒёгҒ¶дәӢгҒ«гӮҲгҒЈгҒҰе®ҹиЎҢгҒ—гҒҫгҒҷгҖӮ

гҒ“гҒ®гҒЁгҒҚеҗҢжҷӮгҒ«гҖҒеј•гҒҚеҮәгҒ—гӮ’иЎҢгҒҶгҒҹгӮҒгҒ«гҒҜгҖҢгғ•гӮЎгғігӮўгӮҰгғҲгӮӘгғ—гӮ·гғ§гғігҖҚз”»йқўгҒ® [гғ•гӮЎгғігӮўгӮҰгғҲеҫҢгҒ«йғЁе“ҒеӨ–еҪўгҒҫгҒ§й…Қз·ҡгҒҷгӮӢ] гӮ’жңүеҠ№гҒ«гҒ—гҒӘгҒҸгҒҰгҒҜгҒӘгӮҠгҒҫгҒӣгӮ“гҖӮгҒ“гҒ®иЁӯе®ҡгӮ’иЎҢгӮҸгҒӘгҒ„е ҙеҗҲгҒ«гҒҜгҖҒгғ•гӮЎгғігӮўгӮҰгғҲ (гғ“гӮўгҒ®зҷәз”ҹ) гҒ гҒ‘гҒ§еҮҰзҗҶгҒҢзөӮдәҶгҒ—гҒҫгҒҷгҖӮ

[гғ•гӮЎгғігӮўгӮҰгғҲеҫҢгҒ«йғЁе“ҒеӨ–еҪўгҒҫгҒ§й…Қз·ҡгҒҷгӮӢ] гӮ’жңүеҠ№гҒ«гҒ—гҒҹеҫҢгҖҒ[OK] гғңгӮҝгғігӮ’жҠјгҒҷдәӢгҒ«гӮҲгӮҠгғ•гӮЎгғігӮўгӮҰгғҲгҒҢе®ҹиЎҢгҒ•гӮҢгҒҫгҒҷгҖӮ

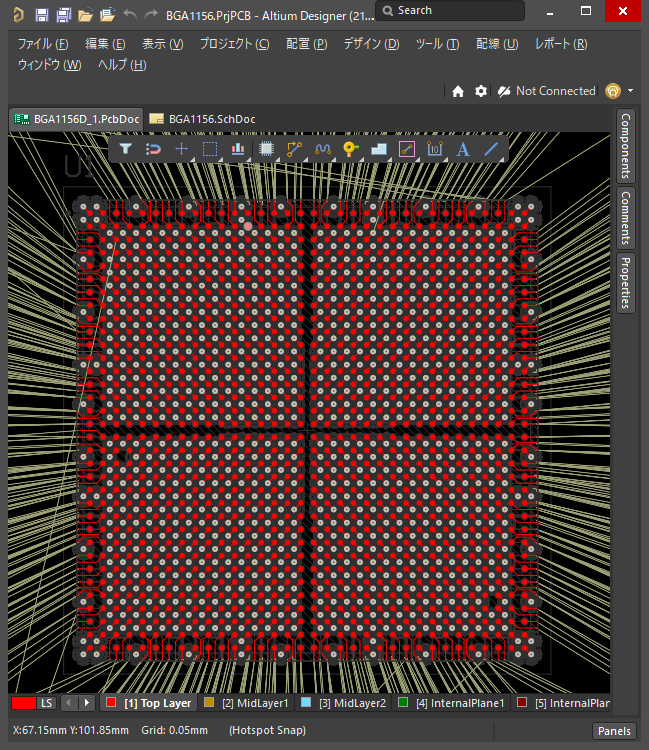

гҒ“гҒ®ж©ҹиғҪгӮ’дҪҝгҒҶгҒЁгҖҒжүӢдҪңжҘӯгҒ§гҒҜдҪ•жҷӮй–“гӮӮгҒӢгҒӢгӮӢдҪңжҘӯгҒҢгҖҒгҒ»гӮ“гҒ®ж•°з§’гҒ§е®ҢдәҶгҒ—гҒҫгҒҷгҖӮ

гҒ“гҒ®з”»йқўгҒҜгҖҒе®ҹиЈ…йқўгӮ’иҰӢгӮ„гҒҷгҒҸгҒҷгӮӢгҒҹгӮҒгҒ«гҖҒгӮ·гғігӮ°гғ«гғ¬гғјгғӨгғўгғјгғүгҒ§иЎЁзӨәгҒ—гҒҰгҒ„гҒҫгҒҷгҖӮгғ©гғғгғ„гғҚгӮ№гғҲгҒ®е§ӢзӮ№гҒҢгҖҒз«ҜеӯҗгҒӢгӮүгғ‘гғғгӮұгғјгӮёгҒ®еӨ–е‘ЁйғЁгҒ«з§»еӢ•гҒ—гҒҰгҒҠгӮҠгҖҒеј•гҒҚеҮәгҒ—гҒҢе®ҢдәҶгҒ—гҒҰгҒ„гӮӢгҒ“гҒЁгҒҢеҲҶгҒӢгӮҠгҒҫгҒҷгҖӮгҒ•гӮүгҒ«и©ігҒ—гҒҸиҰӢгӮӢгҒЁгҖҒе·ҰдёҠд»ҳиҝ‘гҒ«гғ“гӮўгҒӢгӮүгғ©гғғгғ„гғҚгӮ№гғҲгҒҢеҮәгҒҰгҒ„гӮӢз®ҮжүҖгҒҢгҒӮгӮҠгҒҫгҒҷгҖӮгҒ“гҒ®з®ҮжүҖгҒҜеј•гҒҚеҮәгҒ—гҒ«еӨұж•—гҒ—гҒҰгҒ„гҒҫгҒҷгҒҢгҖҒжүӢдҪңжҘӯгҒ§з°ЎеҚҳгҒ«еј•гҒҚеҮәгҒҷдәӢгҒҢгҒ§гҒҚгҒҫгҒҷгҖӮ

еј•гҒҚеҮәгҒӣгҒӘгҒ„з®ҮжүҖгҒҢеӨҡзҷәгҒ—гҒҹе ҙеҗҲгҒ«гҒҜ

иҮӘеӢ•гҒ§еј•гҒҚеҮәгҒӣгҒӘгҒ„з®ҮжүҖгҒҜжүӢй…Қз·ҡгҒ§еј•гҒҚеҮәгҒ—гҒҫгҒҷгҖӮгҒ—гҒӢгҒ—гҖҒгҒ“гҒ®гӮҲгҒҶгҒӘз®ҮжүҖгҒҢеӨҡзҷәгҒ—гҒҹе ҙеҗҲгҒ«гҒҜгҖҒжҲҰз•ҘгӮ’иҰӢзӣҙгҒ—й…Қз·ҡеҜҶеәҰгӮ’дёҠгҒ’гҒӘгҒҸгҒҰгҒҜгҒӘгӮҠгҒҫгҒӣгӮ“гҖӮй…Қз·ҡгҒ®зІҫзҙ°еҢ–гҖҒIVHгҒ®дҪҝз”ЁгҖҒеұӨж•°гҒ®иҝҪеҠ гҒӘгҒ©гҒ®ж–№жі•гҒҢгҒӮгӮҠгҒҫгҒҷгҖӮгҖҢй«ҳеҜҶеәҰгҒӘBGAгҒ®й…Қз·ҡгӮ’е®№жҳ“гҒ«гҒҷгӮӢAltium DesignerгҒ®ж©ҹиғҪгҖҚгҒ§Altium DesignerгҒ®гӮөгғқгғјгғҲгҒҷгӮӢй«ҳеҜҶеәҰеҢ–жҠҖиЎ“гӮ’зҙ№д»ӢгҒ—гҒҰгҒ„гҒҫгҒҷгҖӮ

гҒҫгҒҹгҖҒй…Қз·ҡгӮ’зІҫзҙ°еҢ–гҒҷгӮӢе ҙеҗҲгҒ«гҒҜгҖҒжӯ©з•ҷгҒҫгӮҠгҒ®дҪҺдёӢгӮ’йҒҝгҒ‘гӮӢзӮәгҒ«гҖҒFPGAгҒ®е‘ЁиҫәгҒ гҒ‘гӮ’зІҫзҙ°еҢ–гҒҷгӮӢгҒЁгҒ„гҒҶж–№жі•гҒҢеҠ№жһңзҡ„гҒ§гҒҷгҖӮгҒ“гӮҢгҒ«гҒҜгғ«гғјгғ ж©ҹиғҪгҒҢеҪ№з«ӢгҒЎгҒҫгҒҷгҖӮгҒҫгҒҹгҖҒгғ«гғјгғ гҒ§й ҳеҹҹгӮ’жҢҮе®ҡгҒ—гҒҰгҖҒгӮ№гғҡгғјгӮ№гҒҢи¶ігӮҠгҒӘгҒ„з®ҮжүҖгҒ®й…Қз·ҡгӮ’гғҚгғғгӮҜгғҖгӮҰгғігҒҷгӮӢгҒЁгҒ„дәӢгӮӮгҒ§гҒҚгҒҫгҒҷгҖӮгҒ“гҒ®жүӢй ҶгҒҜгҖҒгғ«гғјгғ гӮ’гӮҲгӮҠжңүеҠ№гҒ«жҙ»з”ЁгҒҷгӮӢгҒ§зҙ№д»ӢгҒ—гҒҰгҒ„гҒҫгҒҷгҖӮгғ«вҖ•гғ гҒ§иЁӯе®ҡгҒ—гҒҹгғҚгғғгӮҜгғҖгӮҰгғігғ«гғјгғ«гҒҜгҖҒиҮӘеӢ•гҒЁгӮӨгғігӮҝгғ©гӮҜгғҶгӮЈгғ–й…Қз·ҡгҒ®дёЎж–№гҒ§еҲ©з”ЁгҒ§гҒҚгҒҫгҒҷгҖӮ

й…Қз·ҡеҜҶеәҰгӮ’дёҠгҒ’гӮӢж–№жі•гҒҜд»–гҒ«гӮӮгҒӮгӮҠгҒҫгҒҷгҒҢгҖҒгҒ„гҒҡгӮҢгӮӮжӯ©з•ҷгҒҫгӮҠгҒЁгӮігӮ№гғҲгҒ«еҪұйҹҝгҒ—гҒҫгҒҷгҒ®гҒ§гҖҒеҹәжқҝгғЎгғјгӮ«гғјгҒЁгҒ®зӣёи«ҮгҒҢеҝ…иҰҒгҒ§гҒҷгҖӮ

е‘ЁиҫәгҒ®гӮігғҚгӮҜгӮҝгҒЁгҒ®жҺҘз¶ҡ

гҒ“гӮҢгҒ§гҖҒд»ҠеӣһгҒ®гғҶгғјгғһгҒ§гҒӮгӮӢBGAгҒ®й…Қз·ҡгҒ®еј•гҒҚеҮәгҒ—гҒҜе®ҢдәҶгҒ—гҒҫгҒ—гҒҹгҒҢгҖҒеҸӮиҖғгҒ®гҒҹгӮҒгҒ«е‘ЁиҫәгҒ®гӮігғҚгӮҜгӮҝгҒёгҒ®й…Қз·ҡгӮ’иЎҢгҒЈгҒҰгҒҝгҒҫгҒ—гҒҹгҖӮBGAгҒЁжҜ”гҒ№гӮӢгҒЁгҖҒгӮігғҚгӮҜгӮҝгҒ®з«ҜеӯҗеҜҶеәҰгҒҢж јж®өгҒ«дҪҺгҒ„дәӢгҒ«еҠ гҒҲBGAгҒЁгҒ®й–“гҒ®й…Қз·ҡгӮ№гғҡгғјгӮ№гӮӮеҚҒеҲҶгҒ«зўәдҝқгҒ•гӮҢгҒҰгҒ„гӮӢгҒҹгӮҒгҖҒгӮӘгғјгғҲгғ«гғјгӮҝгҒ§гҒ»гҒј100%гҒ®й…Қз·ҡгҒҢе®ҢдәҶгҒ—гҒҫгҒ—гҒҹгҖӮ

е®ҹйҡӣгҒ®иЁӯиЁҲгҒ§гӮӮгҖҒе‘ЁиҫәгҒ®еӣһи·ҜгҒ®з«ҜеӯҗеҜҶеәҰгҒҜBGAгӮҲгӮҠгӮӮдҪҺгҒ„гҒ®гҒҢжҷ®йҖҡгҒ§гҒҷгҒ®гҒ§гҖҒBGAгҒӢгӮүгҒ®еј•гҒҚеҮәгҒ—гҒҢеҸҜиғҪгҒ§гҒӮгӮҢгҒ°гҖҒй…Қз·ҡгҒҜйӣЈгҒ—гҒҸгҒӘгҒ„гҒҜгҒҡгҒ§гҒҷгҖӮ

гӮӘгғјгғҲгғ«гғјгӮҝгҒ§й…Қз·ҡгҒ—гҒҹеҫҢгҖҒжңӘзөҗз·ҡгҒӘгҒ©ж•°гҒӢжүҖгӮ’жүӢдҪңжҘӯгҒ§дҝ®жӯЈгҒ—гҒҫгҒҷгҖӮ

гҒ“гҒ®гӮҲгҒҶгҒ«гҖҒгғ•гӮЎгғігӮўгӮҰгғҲгғ»гғ«гғјгғҶгӮЈгғігӮ°ж©ҹиғҪгӮ’дҪҝгҒҶгҒЁгҖҒ1000гғ”гғігӮ’и¶ҠгҒҲгӮӢBGAгҒ§гӮӮж•°з§’гҒ§еј•гҒҚеҮәгҒ—гҒҢе®ҢдәҶгҒ—гҒҫгҒҷгҖӮгғ•гғ¬гӮӯгӮ·гғ–гғ«гҒӘгғ«гғјгғ«иЁӯе®ҡж©ҹиғҪгҒӘгҒ©гӮ’дҪөз”ЁгҒҷгӮӢгҒ“гҒЁгҒ«гӮҲгӮҠгҖҒй«ҳе“ҒиіӘгҒӘBGAеҹәжқҝгҒ®иЁӯиЁҲгӮ’зҹӯжҷӮй–“гҒ«зөӮгҒҲгӮӢдәӢгҒҢгҒ§гҒҚгҒҫгҒҷгҖӮ

д»ҠгҒҷгҒҗAltium DesignerгҒ®з„Ўе„ҹи©•дҫЎзүҲгӮ’гғӘгӮҜгӮЁгӮ№гғҲгҒ—гҒҰгҖҒдё–з•ҢжңҖй«ҳгҒ®PCBиЁӯиЁҲгӮҪгғӘгғҘгғјгӮ·гғ§гғігӮ’гҒҠи©ҰгҒ—гҒҸгҒ гҒ•гҒ„пјҒгҒ”дёҚжҳҺгҒӘзӮ№гҒӘгҒ©гҒ”гҒ–гҒ„гҒҫгҒ—гҒҹгӮүгҖҒгҒҠе•ҸгҒ„еҗҲгӮҸгҒӣгғ•гӮ©гғјгғ гҒ«гҒ”е…ҘеҠӣгҒҸгҒ гҒ•гҒ„гҖӮ