高密度なBGAの配線を容易にするAltium Designerの機能

端子数の多いLSIでは、BGAパッケージが良く利用されます。このBGAは、端子の密度が高いのでパッケージを小さくでき、小型化が求められる携帯機器に最適です。しかし、密集した端子の周辺にはわずかなスペースしか残っておらず、全ての端子から配線を引き出すのは至難の業です。これは、高密度な端子配列の代償として突き付けられた課題であり、端子密度に見合うところまで配線密度をあげる事しか解決の道はありません。

そこで、今回はこの高密度な配線を可能にするAltium Designerの機能を紹介したいと思います。

BGAパッケージは、普及し始めてから20年以上経ちます。今では携帯機器に当たり前のように使われており、その特徴は皆さんご存知のはずですが、今回は念のため要点のおさらいから始めたいと思います。

BGAパッケージについて

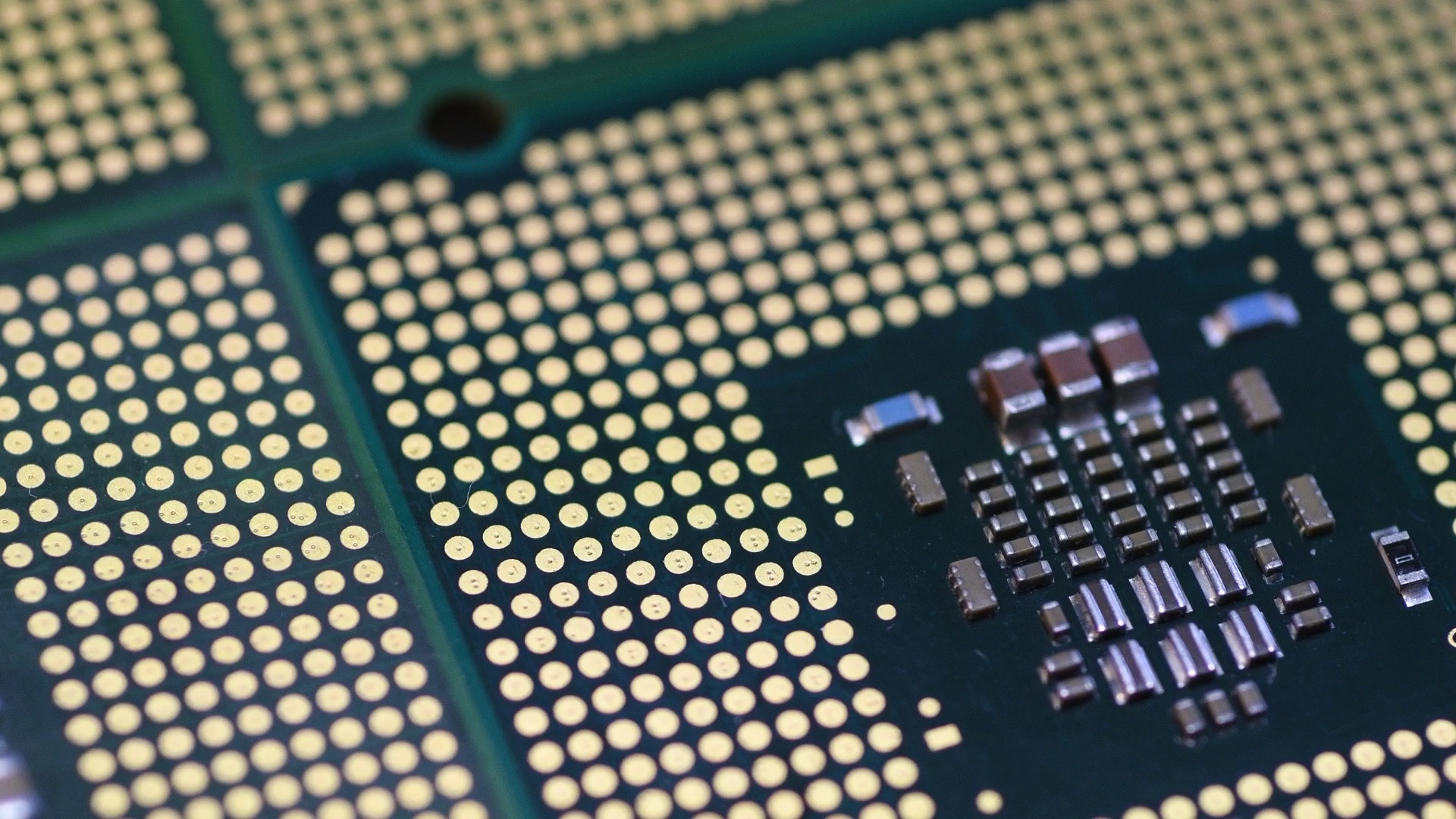

BGAパッケージはBall Grid Arrayの略でその名の通り、格子上に配置されたボール状の端子を持つ表面実装部品です。

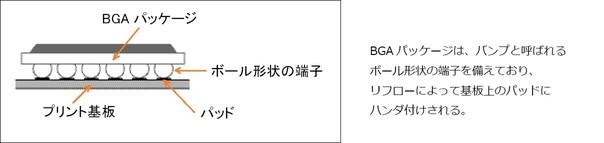

端子数は、20以下のものから2000を越えるものまであります。端子の間隔は、1.5mm、1.27mm、1.0mm、0.8mm、0.65mm、0.5mmのものがあります。また、端子の配列は、パッケージの中心部付近に端子が無いものと、端子面の格子上の全てが端子で埋め尽くされたフルグリッドのものがあります。

BGAは、それまで高密度実装用として使用されてきたPGAやQFPに対して、さらに実装密度を上げるためのものです。構造的にみてもPGA端子の格子配列とQFPの表面実装の特徴が組み合わさったものであるといえます。

200ピン近辺の端子を持つ各パッケージのサイズを比較。1mmピッチ、256ピンのフ端子を持つルグリッドのBGAと、一般的な端子配列の223ピンPGAとを比較すると占有面積に約8倍の差があります。

BGAの配線は極めて困難

BGAパッケージを使うと実装密度を飛躍的に高めることができますが、配線は困難になります。BGA端子の周りは、配線の経路を見つけ出すのが難しいだけでなく、実際に線を置いていくのにも多くの手間がかかります。それは、次のような理由によるものです。

BGAは表面実装

BGAは、基板を貫通する端子を持たないので、実装面以外の層では端子に直接、接続する事はできません。このため、実装面以外の層との接続には必ず、VIA(ビア)を配置しなくてはならず、このVIAが配線スペースを浪費します。

BGAは狭い間隔で端子が何列も並んでいる

QFPパッケージも狭い間隔で端子が並んでいますが、BGAはQFPのように一列ではなく何重にも並んでいます。この為、外側の端子の配線が内側端子からの引き出しの邪魔になり、簡単には外に引き出せません。

BGAは端子が多い

BGAパッケージでは500ピンは当たり前で、その何倍もあるものも珍しくありません。それだけ端子数が多いと配線経路が見つかった後の機械的な配線作業にも、多くの手間がかかってしまいます。

例えば、600本の端子から配線を引き出す場合、ひとつの端子の配線が10秒で終わったとしても、合計100分(1時間40分)の時間がかかってしまいます。実際には、試行錯誤が必要な場面も出てきますので、もっと時間がかかるでしょう。

BGAは高速な回路に使われる事が多い

BGAパッケージは、高速で動作する回路で使われる事が多く、配線パターンの伝送特性のコントロールを求められる事がよくあります。

このように、BGA周りの配線は難易度が高く、CADツールによる高度なサポートが欠かせません。

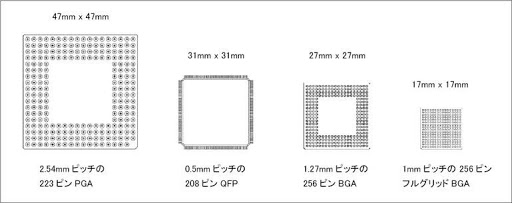

QFPの場合、端子はパッケージの外周部に一列に並んでいるだけなのでVIAやパッドを使わずに配線を引き出す事ができます。一方、BGAでは、外周から2列目まではVIAやパッドは不要ですが、3列目より内側では必要になります。

高密度な配線を可能にするAltium Designerの機能

Altium Designerは高密度な配線を可能にする多くの機能を備えています。特に、BGAパッケージを使う場合には、これらの機能が役立ちます。

48層までの多層基板の設計が可能

BGAを使う場合には、多層化が避けられません。

Altium Designerでは、32の配線層に加え16のプレーン層をサポートしています。端子数の多いBGAの配線には多くの配線層が必要になりますが、2000ピン程度のBGAでも10層あれば引き出しが可能ですので層数が不足することはありません。

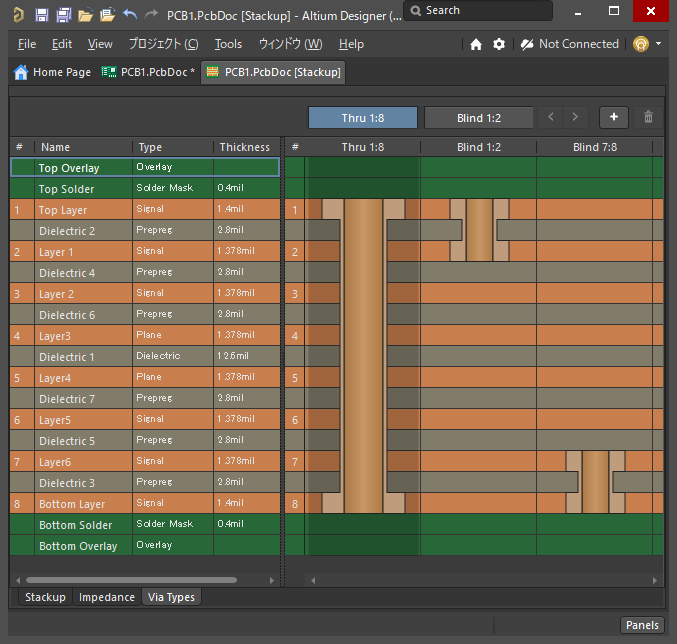

埋め込みVIAをサポート

全層を通過する貫通VIAでは、接続が不要な層にも導体と穴が存在し、これらが貴重な配線スペースを浪費します。一方、埋め込みVIAは、接続を行う層と層の間だけにスルーホールを生成しますので、配線スペースが無駄に圧迫される事はありません。

埋め込みVIAは、IVH(Interstitial Via Hole)と略して呼ばれます。また、VIAの片側が基板の表面に現れているものを、ブラインドVIA、内層間の接続に使用され外から見えないものをベリードVIAと呼んでいます。そして、Altium Designerはこれらの全てをサポートしています。

一般的な多層基板では、加工済の2層基板を積み重ねるという工法が用いられる為、IVHで接続可能な相手の層が制限されます。

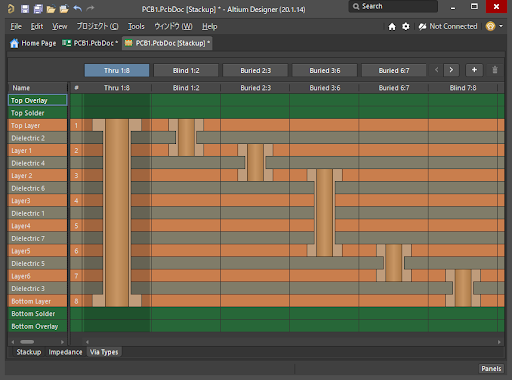

ビルドアップ基板に対応

Altium Designerは、ビルドアップ基板をサポートしています。

通常、IVHを使用する多層基板は、コア材と呼ばれる両面基板を必要な層数が得られるまで重ね合わせて作成されます。例えば、6層のIVH基板の場合には3枚のコア材を貼り合わせます。

この工程では、コア材を加工する時にVIAを形成しますので、IVHは一枚のコア材の2層間にしか作成することができません。CADによる設計工程では、このコア材単位の2層をドリルペアと呼んでいます。

一方、ビルドアップ基板では、1層単位で配線パターンを積み上げていきますので、ドリルペアによるVIAの制限がなく、任意の層間にIVHを使用することができます。また、VIAのサイズも小型化できるため、VIAによるスペースの浪費を防ぐことができます。

ビツドアップでは、1層ごとに導体を形成していく為、IVHで接続できる層の組み合わせに制限は生じません。

パッドオンVIAをサポート

Altium Designerは、パッドオンビアをサポートしています。

通常、基板上のVIAの中央には穴が開いており、表面には凹凸があります。このため、VIAの上にBGAの端子を乗せてハンダ付けすることができません。

一方、パッドオンVIAではこのVIAの穴を埋めて表面を平坦にすることにより、VIAをBGA端子をハンダ付けする為のパッドとして利用できます。このパッドオンVIAを用いるとVIAとBGAパッドを共用できるため、スペースを大幅に節約できます。

BGAの配線が困難な理由のひとつとして、BGAが表面実装部品であることをあげましたが、このパッドオンVIAを使用する事により、BGAをリード付き部品と同じように配線する事ができます。

ネックダウン配線

Altium Designerでは、Room (ルーム)毎にデザインルールを設定する事ができます。

この機能を使って、BGA端子周りの線幅だけを他より狭く(細く)設定する事によって、配線が自動的にネックダウンし、端子間に配線が通り易くなります。

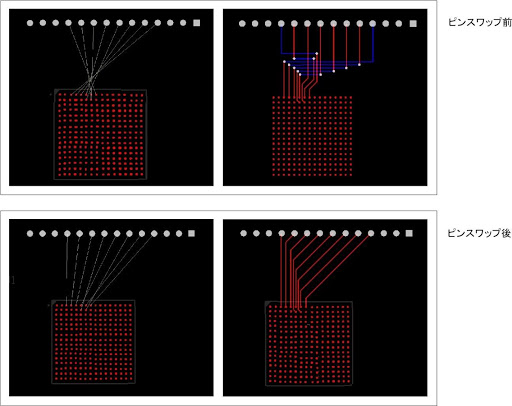

ピンスワップ

FPGAでは、I/O端子に対する信号の割付を自由に決める事ができます。この為、基板上に配置したあと、配線の交差が少なくなるように端子配列を変更する事ができます。Altium Designerは、これを自動的に行う事ができる、ピンスワップ機能を備えています。

この機能は、他のタイプのパッケージを使う場合にも役立ちますが、端子密度の高いBGAでは特に有用です。

ピンスワップ機能によって配線長を最短化したり、配線の交差を解消したりする事ができます。

BGA端子からの引き出しを自動的に行うBGAファンアウト・エスケープ機能

Altium Designerは、BGA周りの配線に欠かせないBGAファンアウト・エスケープ機能を備えています。一口に言うと、これは自動配線機能です。また、これは、ここまでに紹介したような高密度化の為の機能では無く、配線に費やす時間を節約する為のものです。

この機能を利用すると、自動的に引き出しパッドが発生し、BGAパッケージの周囲に配線が引き出されます。手設計では何時間もかかるBGAからの引き出し配線が、この機能を使うと数秒で完了します。

ここで紹介したAltium Designerの機能によって、BGA周り配線密度を上げると共に設計時間を短縮する事ができるはずです。もし、まだ利用していない機能があるようでしたら、ぜひ一度お試しください。

今すぐAltium Designerの無償評価版をリクエストして、世界最高のPCB設計ソリューションをお試しください!ご不明な点などございましたら、お問合せフォームにご入力ください。