HDI設計の基本

HDI設計の基本について説明します。HDI設計を計画する場合、HDIプロセスの性能を測る基準または指標があります。作成: Happy Holden

相互接続の密度の定義

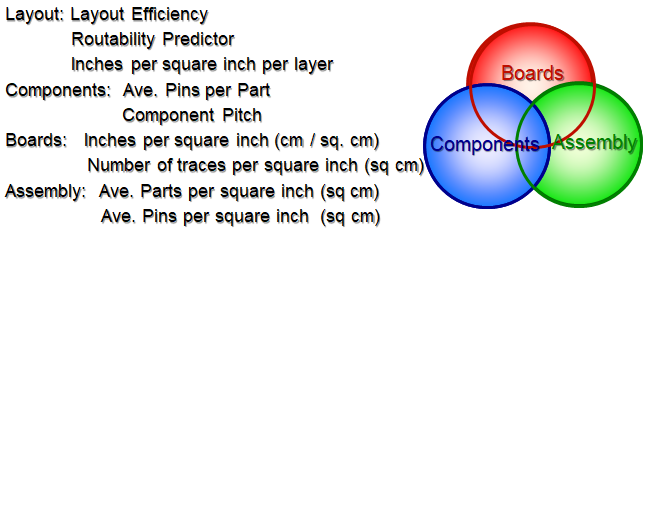

HDI設計を計画する場合、HDIプロセスの性能を測る基準または指標があります。図1の三角形に示すように、HDIプロセスに不可欠な3つの輪が配線密度の要素となります。

図1. HDI設計指標

Alt text: HDI設計指標のスクリーンショット

アセンブリの複雑さ

表面実装部品のアセンブリの難しさを示す2つの指標は、平方インチ(または平方cm)当たりの部品数で測定される部品密度(Cd)と平方インチ(または平方cm)当たりのリード数で測定されるアセンブリ密度(Ad)です。

部品のパッケージング

部品の複雑さを示す指標は、部品当たりの平均リード(I/O)数で測定される部品の複雑さ(Cc)です。もう1つの指標として、部品のリードピッチもあります。

プリント配線基板の密度

基板の平方インチ当たりの平均トレース長(全信号レイヤーを含む)で測定されるプリント回路の密度(複雑さ)(Wd)です。この指標の単位は平方インチ当たりインチ(または平方cm当たりcm)です。第2の指標としてリニアインチ(またはcm)当たりのトレース数もあります。PWB密度は、「ネット当たり平均3つの電気的ノードがあり、部品のリードはネットのノードである」という仮定の下で導かれており、平方インチ当たりの部品数と部品当たりの平均リード数の積の平方根に比例するという式になっています。は2.5(アナログ/ディスクリート領域)、3.0(アナログ/デジタル領域)、3.5(デジタル/ASIC領域)です。

PWB密度(Wd) = √ [Cd] x [Cc]

= √ [平方インチ当たりの部品数] x [部品当たりの平均リード数]

ここで、 p = 部品数(個)

l = 全部品のリード数

a = 基板の上面の面積(平方インチ)

パッケージング技術マップ

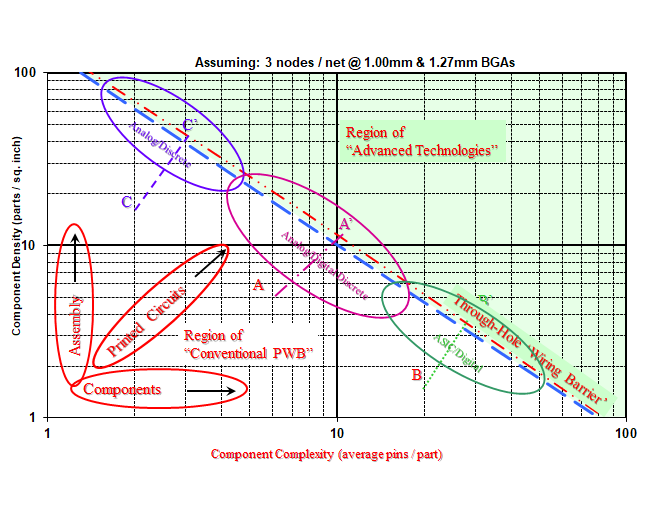

図2は、パッケージング技術マップと呼ぶものです。パッケージング技術マップは、1991年1月に東芝が初めて示しました。[1]

このマップの2番目に重要な機能は右上の領域です。この「高度な相互接続の領域」で、HDI構造が必要です。破線がHDIの限界または壁です。これを越えると初めて、HDIを使うことのコスト効率が高くなります。破線から大きく離れると、HDIを使うことが不可欠になります。

図2. 一般的なアセンブリの機能としてのスルーホール(TH)配線の障害

Alt text: スクリーンショット

パッケージング技術マップは、アセンブリのサイズ、部品数、部品のリード数を測定することで作成します。部品には、アセンブリの両面とedge finger、またはcontactが含まれます。単純にリード数を部品数で割った数と部品数をアセンブリ面積で割った数とで、X軸とY軸とが分かります。部品当たりの平均リード数に対する平方インチ(cm)当たりの部品数を両対数グラフ上にプロットすると、PWB配線密度(平方インチ(cm)当たりのインチ(cm))とアセンブリの複雑さ(平方インチ(cm)当たりのリード数)が計算できます。アセンブリ密度は単純にX軸とY軸の積です。

スルーホール配線の限界

チャート(図 2)を使って表面実装アセンブリを分析すると、パッケージングチャートに3つの主要な領域があるのが分かります。そのため、これをマップと呼んでいます。第1のグループは、アナログデバイスとディスクリート部品を多く含む製品です。典型的な製品は、ビデオカメラ、ポケットベル、携帯電話です(C-C’)。これらのアセンブリは最も複雑で、平方インチ当たり最大300 ~ 400リード(平方cm当たり47リード)です。第2のグループは、多くのデジタル部品にディスクリート部品を部分的に組み合わせた製品です。例えば、ノートPC、デスクトップPC、計測器、医療機器、通信ルーターがあります(A-A ')。第3のグループは、ICを高密度で使うものです。PCMCIA、フラッシュメモリ、SiP、その他のモジュールがこのグループの典型です(B-B’)。このグループのPWB配線密度は最も高く、平方インチ当たり160インチ(平方cm当たり25cm)を超えます。図は大まかにこの3つの領域を示しています。

図を見ると、アセンブリの複雑さの線が配線密度の線と交差しています。ディスクリート部品が多い場合、一定のアセンブリ密度に対して必要な配線は少なくなります。ASICが多くディスクリート部品が少ない場合、部品を接続するのにさらに多くの配線が必要です。したがって、平方インチ当たりリード数などのアセンブリ指標は適切な指標になりますが、PWB配線密度の代わりには不向きです。

プリント基板設計の一般的なプロセス

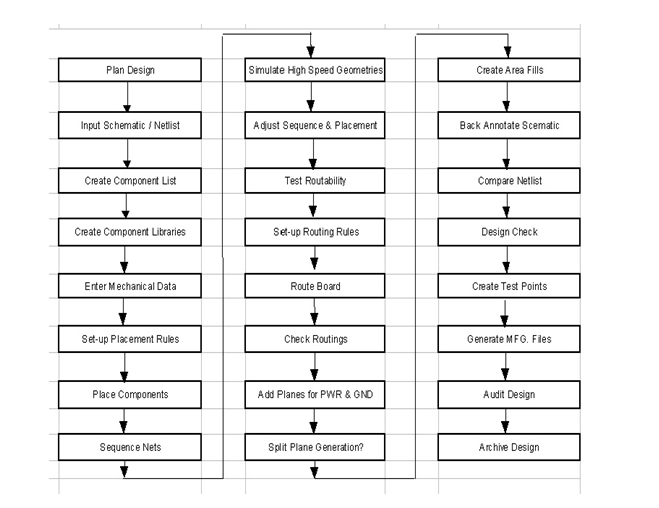

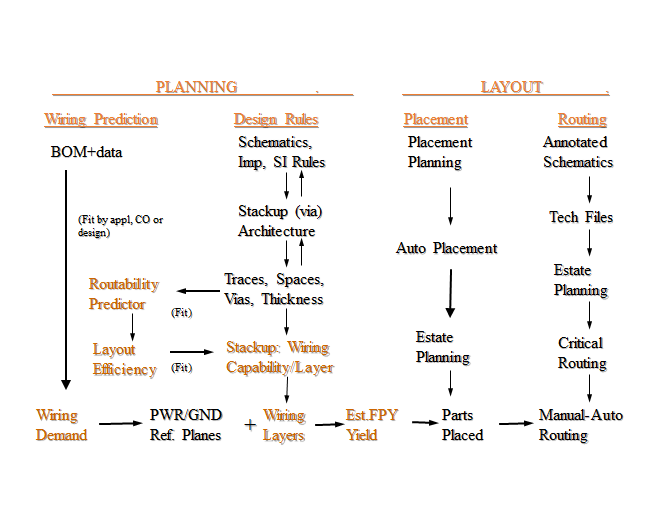

図3に、HDIテクノロジーを利用したプリント基板設計のプロセスを示します。HDIテクノロジーを使って設計する場合、第1の段階 – [設計計画]は最も重要です。図4に示すように、HDIの配線効率はスタックアップ、ビア アーキテクチャー、部品配置、BGAファンアウト、設計ルールで決まります。しかし、製造歩留まり、アセンブリに関する考慮事項、インサーキット テストを含むHDIの価値の提供の連鎖全体を考慮する必要があります。PWBの製造業者、組み立て業者との連携は、設計を成功させるのに不可欠です。

図3. プリント基板設計とレイアウトプロセスの概要

Alt text: スクリーンショット

HDI規格、ガイドライン、仕様、参考文献

HDI設計を始める場合、出発点はIPCガイドラインおよび規格です。図5に示すように、HDI設計には特に4つが適用されます。

図4. 一般的なプリント基板設計プロセスを追加するHDI計画の推奨プロセス

Alt text: スクリーンショット

- IPC/JPCA-2315: これはHDIの概要であり、設計の密度を推定するためのモデルを提供します。

- IPC-2226: この仕様は、マイクロビアの形成、配線密度の選択、設計ルールの選択、相互接続の構造、材料の特性評価を理解する上でユーザーの参考になります。マイクロビアテクノロジーを利用したプリント回路基板の設計で使う基準を提供することを目的としています。[2]

- IPC-4104: この規格は、高密度相互接続構造に使用される材料を特定します。IPC-4104 HDI材料仕様には、HDIに使用される薄膜材料の多くを定義するスラッシュシートが含まれます。材料特性のスラッシュシートは3つの主な材料タイプ(誘電絶縁体(IN)、導体(CD)、導体と絶縁体(CI))に分かれています。

- IPC6016: この文書では、高密度構造の性能と評価について説明しています。

図5. IPC規格、およびガイドライン

Alt text: スクリーンショット

HDI設計の特徴

3つの新しい原則

HDIマイクロビア設計には、スルーホール設計にはない以下の3つの新しい原則があります。

- マイクロビアはTHビアを置き換える必要がある。THビアに「追加」するだけではない

- THビアを削除できるように新規のレイヤースタックアップを検討する

- 配線しやすいように、チャンネルと配線スペースができるような方法でマイクロビアを配置する(表1参照)

スルーホール(TH)を置き換えるマイクロビア

主な考え方は、マイクロビアでTHビアを置き換える(THビアを削除できる)ということです。結果として、THビアが占めていたスペースを使うことで内層の配線密度を2倍または3倍に向上できます。これにより、信号層とその信号層のリファレンスレイヤーを減らせます。

この原則は初めの印象より難解です。これは、マイクロビアの配置方法に3つの次元があるためです(図6参照)。

表1. THマルチレイヤーを使わないHDI設計の新しい原則

- ブラインドビアは、X-Yまたはθ角で「シフト、またはスイング」することで配線スペースを広げることができる

- ブラインドビアを内層(3D)に配置することでブレークアウトスペースを広げることができる

- トレースのスペースを広げるため、中心間距離を内層で変えることができる

- 基板の一次側またはその近くで上記を行った場合、基板の二次側のBGAの下部にトレースのための、またはより重要なデカップリングコンデンサーのようなディスクリート部品のためのスペースができる