xSignalによる高速伝送路のサポート

高速伝送路では、反射による信号の劣化を避ける為にさまざまな配慮が必要です。

まず、伝送路の特性インピーダンスを整合させる事が必要です。配線パターンのフィジカル(トラックの幅と間隔・プレーンとの間隔)に一貫性を持たせ、ビアなどのスタブ要素を最小限に留めます。そして、電流ループ内のインピーダンスを全て整合させるため、必要に応じてダンピング抵抗(送端終端抵抗)や終端抵抗(遠端終端抵抗)を入れます。

そして、最適な配線トポロジーを選ぶことも重要です。高速回路では一筆書きが基本とされていた時期もありましたが、近年では配線の分岐が避けられないケースが増え、T分岐型のトポロジーがよく用いられるようになってきています。このT分岐型のトポロジーでは、複数の終端に対して対称に配線を行う事が求められます。

デザインルールによる高速伝送路のサポート

Altium Designerは、このような高速伝送路の配線をサポートする機能を数多く備えています。例えば、等長配線や差動ペア配線ツールを備えており、さらに配線品質を検証するためのSIツール(伝送線路シミュレータ)も用意されています。そして、これらの配線・検証機能はハイスピードルールと呼ばれる、高速伝送路に特化したデザインルールによって精密に管理されています。

このハイスピードルールには、Parallel Segment(並行線長の制限)Length(配線長の制限)Matched Length(配線長の統一)を始め8種類の項目が用意されています。

また、デザインルールチェック機能の一部としてSIツールが組み込まれています。このSIツールの制約条件もデザインルールチェックの設定画面で規定する事ができます。

高速伝送路に特化したデザインルールが8種類用意されています。[xSignal] や [xSignal Class] をルールスコープとして利用できます。また、SIツールが組み込まれており、SI検証の結果がデザンルールチェックの基礎データとして利用されます。

xSignalによる高速伝送路のサポ-ト

Altium Designerは、xSignal と名付けられた独自の機能で高速伝送路の配線をサポートしています。この機能により、ネットを複数のパス(経路)に分解して、より詳細にデザインルールの適応範囲を指定できます。

例えば、xSignalを利用しない場合には、ルールスコープの最小単位はネットになります。しかし、ネットには複数の受信端(信号を受け取る側のノード)が含まれている場合があります。このような場合、高速伝送路では、複数の受信端への配線を(同電位であったとしても)それぞれ別の配線パスと見なさなくてはなりません。例えば、CPUに対して4個のメモリが接続されている場合には、1つのネットではなく4つの配線パスとして各メモリに到達する信号を管理しなくてはなりません。

xSignalはこれを可能にします。また、ダンピング抵抗を挿入する場合があります。この場合には、伝送路が2つのネットに分割されてしまいますが、xSignalによってひとつの配線として管理する事ができます。

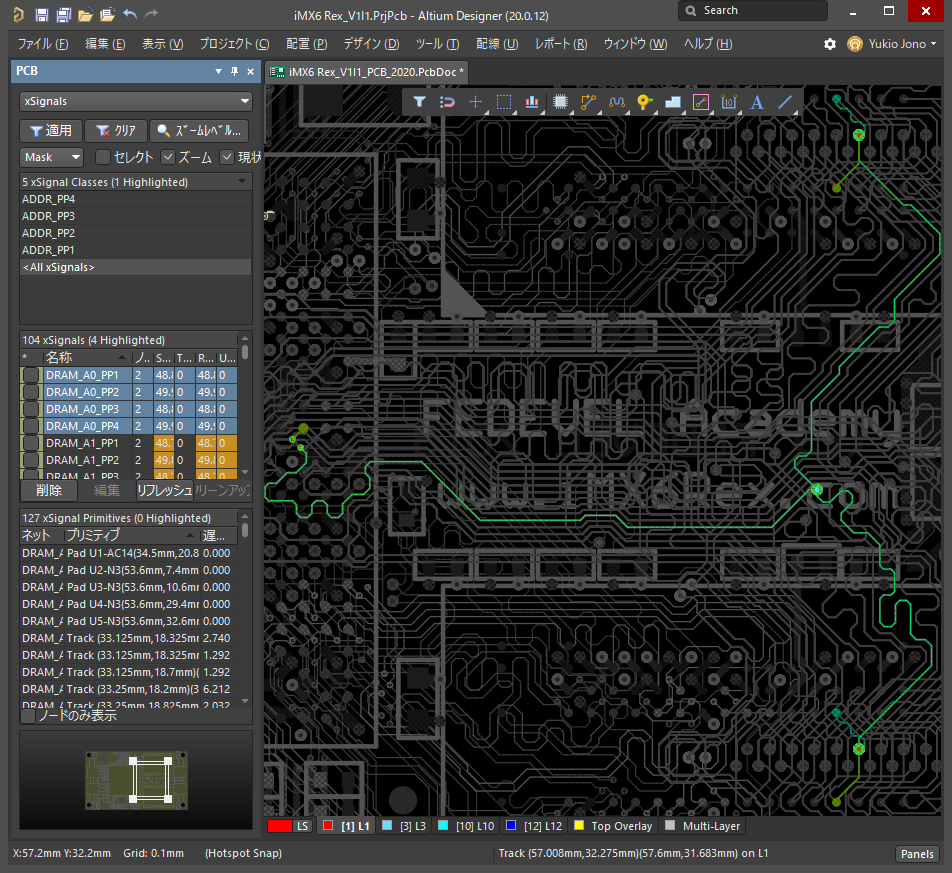

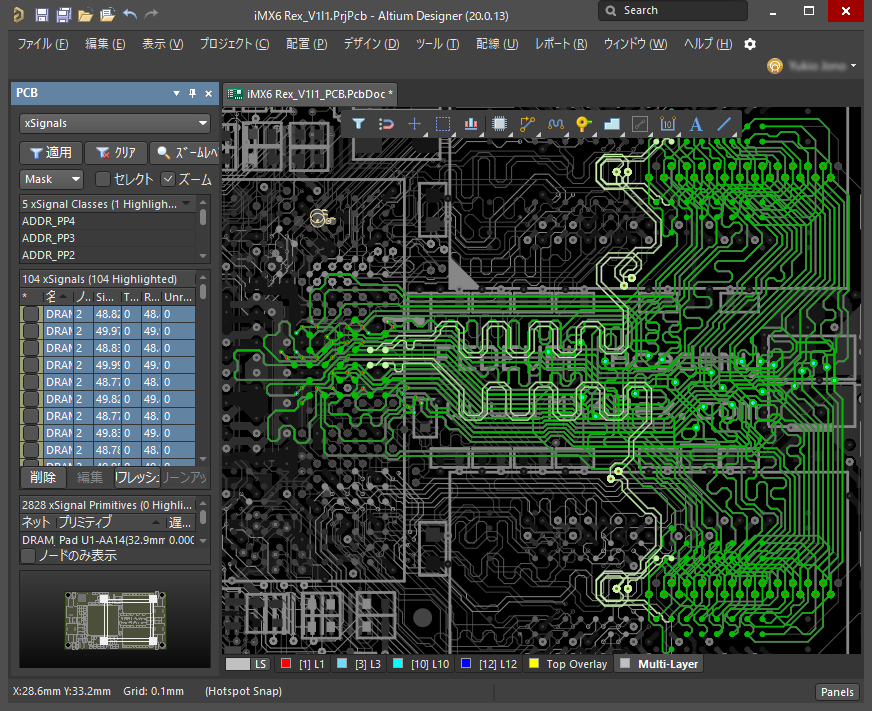

[xSignal ウィザード]でxSignalを自動作成した後、PCBパネルにリストされた4つのxSignalを選択してDRAM_A0ネット全体をハイライトさせた状態。この基板では、CPUに4個のDRAMが接続されているので、DRAM_A0ネットには4つの配線パスが存在します。よって、DRAM_A0ネットからはDRAM_A0_PP1、DRAM_A0_PP2、DRAM_A0_PP3、DRAM_A0_PP4の4つのxSignalが生成されます。この4つのxSignalを全て選択する事によりDRAM_A0ネット全体がハイライトされます。一見すると、T分岐は一ヶ所に見えますが、DRAMが基板の両面に実装されており、一度T分岐した後、再度、上下のDRAMに向けてT分岐しています。生成されたxSignal、又はxSignal Class をルールスコープとして利用する事により、ハイスピードルールを緻密に規定する事ができます。

xSignalを作成する

xSignalは2つのノード間の配線パスであり、高速伝送路の基本単位として編集や検証には欠かせません。このxSignalはマニュアル、またはウィザードで作成する事ができます。そこで、その最も手軽な手段としてxSignalウィザードによる作成手順を紹介します。

1. xSignalウィザードを起動

メニューから [デザイン] - [xSignal] - [xSignalウィザードを実行] を選びます。

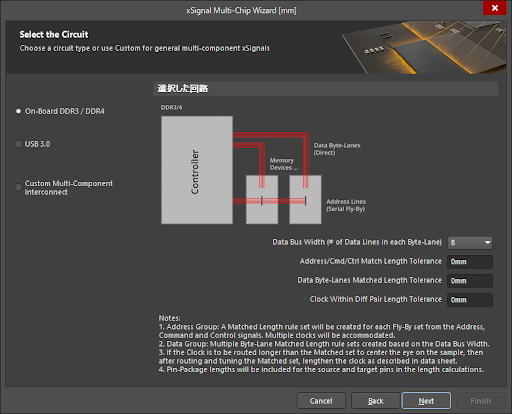

2. 回路の種類を選ぶ

起動直後に表示される開始画面の[Next]ボタンを押すと、[Select The Circuit] ダイアログボックスが表示されます。そこで、[On-Board DDR3 / DDR4] を選び [Next] ボタンを押します。

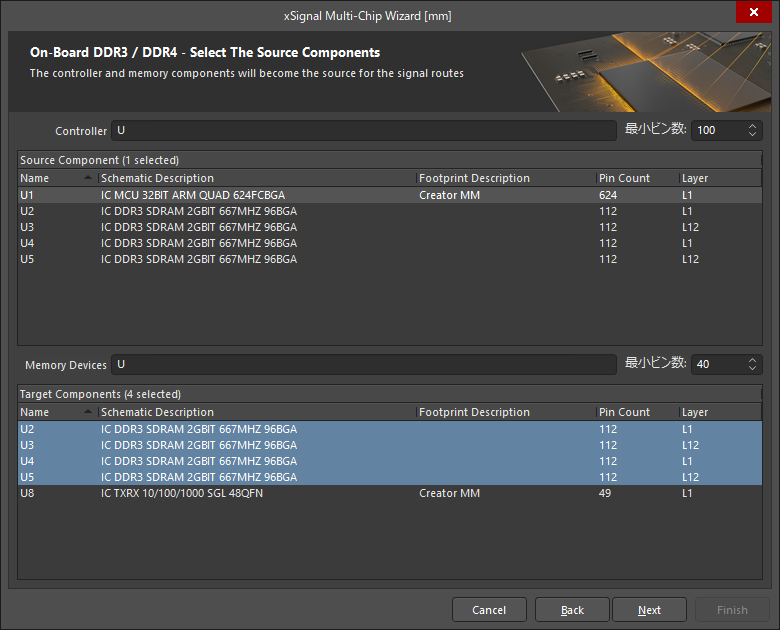

3. 送信デバイスと受信デバイスを指定

[On-Board DDR3 / DDR4 - Select The Source Components ] 画面の [Controller] エリアに表示されたICのリストから、送信デバイスとして [U1 (MCU 32BIT ARM QUAD624FCBGA)] を選びます。そして、[Target Components] エリアのリストから [U2、U3、U4、U5] (SDRAM)を選び、[Next] ボタンを押します。

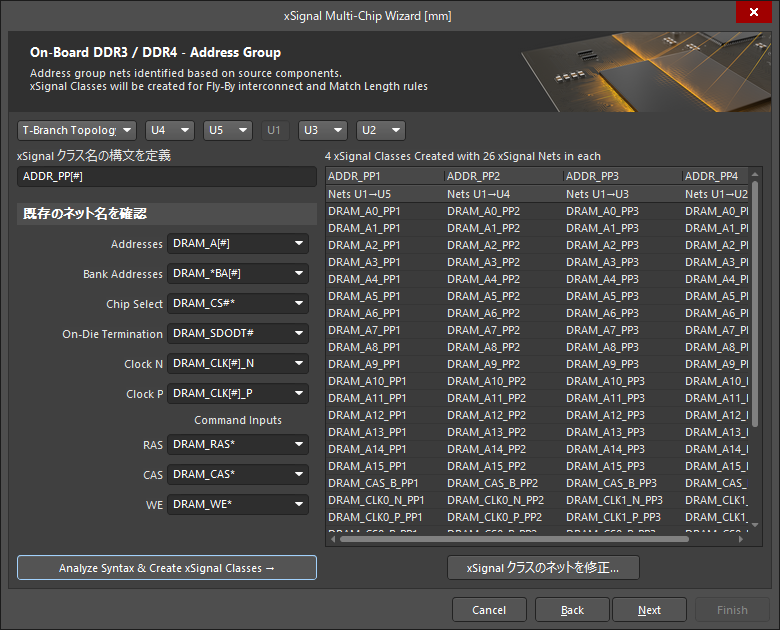

4. アドレス/制御ラインのxSignalを抽出

[On-Board DDR3 / DDR4 - Address Group ] 画面でアドレス/制御信号ラインのxSignalの抽出と編集を行います。[Analyze Syntax & Create xSignal Classes ] ボタンを押すと、xSignal クラスが抽出され画面の右側に表示されます。[xSignal クラスのネットを修正…] ボタンで内容を修正できます。今回は修正せず、[Next]ボタンを押して次に進みます。

5. データラインのxSignalを抽出

[On-Board DDR3 / DDR4 - Data Group ] 画面で、データラインのxSignalの抽出と編集を行います。[Analyze Syntax & Create xSignal Classes ] ボタンを押すとxSignal クラスが抽出されますが、今回は抽出せず、[Finish] ボタンを押します。

6. xSignalの生成

[On-Board DDR3 / DDR4 - Data Group ] 画面の [Finish] ボタンで手続きが完了し、xSignalが生成されます。[PCB] パネルにその内容が表示され、内容の編集と画面表示のコントロールができます。

[xSignal ウィザード] で作成したアドレス/制御ラインを全てハイライトさせた状態

Altium Designerでの基板設計について詳細は、アルティウムのエキスパートにお問い合わせください。