PCIe 5.0のレイアウトと配線について

PCI-SIGは、プロセッサーとコンピューター周辺機器との間の標準化されたデータ速度の限界を引き上げるための作業を行ってきました。この標準化グループはコンポーネントの開発を直接、行ってはいませんが、2019年にPCIe 5.0仕様が公開され、2021年にはPCIe 6.0仕様が公開されるのは、大量のデータを使用するアプリケーション用の周辺機器を標準化するという明確な意図に基づくものです。一部のアプリケーションには、データセンターにおけるAI、5G、超高速NICなどが必然的に含まれます。

PCIe 4.0から5.0への移行によりデータ速度が2倍になったことで、ICやパッケージ設計者の作業は既に困難になっていますが、同時にPCBや嵌合コネクタの問題も複雑化しています。こうした複雑化はすべて、PCIeの世代が新しくなるたびに信号の帯域幅が引き上げられることが原因です。ここでは、PCB設計者がPCIeデバイスを設計するとき、これらの帯域幅による困難に対応する方法を紹介します。

PCIe 5.0レーンでの損失

他の高速インターフェースと同様に、PCIeでもレイアウトと配線に固有の課題がいくつか存在します。トレース、ICのI/O、コネクタ、さらには基板の材質により、基板で損失を仕様範囲内に抑えながら対応可能な帯域幅が制限されます。このブログでは、これまで各種の損失のメカニズムについて解説してきたため、高速チャンネル (PCIeレーンを含む) における重要な損失源について、ここで簡単に要約します。

- 導体損失: 導体の断面に固有のDC抵抗が含まれます。

- 絶縁体損失: PCB基板の励起と緩和により、高速チャンネルを通過する電界が減衰します。

- 銅線の不均一による損失: PCBに積層されたエッチングの銅箔には必ず不均一性 (電気溶着と圧延のどちらでも) があり、インピーダンスを計算するときは銅箔の不均一性を正しくモデル化する必要があります。

- 共鳴電力損失: このファイバー織り込み効果は、緩いファイバー織り込みに周期的な負荷がかかることにより発生し、基板の空洞が励起され、特定周波数に電力損失が引き起こされます。

基板が厚めの場合 (例: John Coonrodによるこの技術記事では30mils) はマイクロストリップでの放射損失も考慮する必要があることに注意してください。しかし、閉じた導波路やストリップライン配線では、これらの損失は無視できます。層数が多い基板や、積層が非常に薄いマイクロストリップでも、これらの損失を無視できます。PCIe 5.0のデータ速度は32Gbpsなので、FR4は現実的な選択肢ではなくなり、低損失の積層を使用する必要があります。

PCIe 5.0のチャンネルでは、絶縁体と不均一性による損失は、適切な低損失の積層を選択することによりPCB基板レベルで対処できます。嵌合コネクタとビアにも固有の損失があります。これは通常、信号の帯域幅内でのインピーダンス不一致による反射から引き起こされます。PCIe 5.0の仕様では、レーンのナイキスト周波数 (ビット速度が32Gbpsなら16GHz) において損失が-37dBに制限されています。1つまたは複数の基板にコンポーネントをどのように配置するかによって、PCIe 5.0のレイアウトと配線で使用できるビアやコネクタの数と、相互接続の最大長が決定されます。

レイアウトと配線のオプション

トポロジーとコネクタ

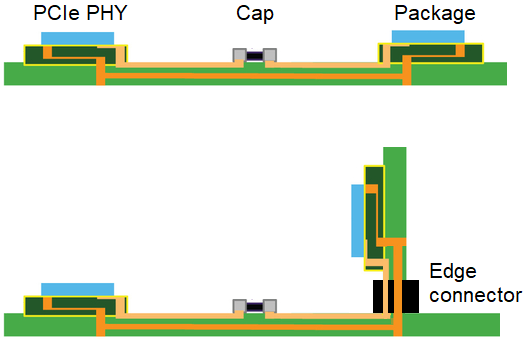

PCB基板の材質を決定し、損失が十分に小さくなるようトレースを設計したら、PCIeデバイスの配線とレイアウトを行います。PCIeデバイス、ドーターボード、ホストプロセッサーは、Point-to-pointのトポロジーで配置されます。PCIe PHYモジュール、デバイス、プロセッサーは同じ基板に配置することも、コネクタ (直交、エッジ、mezzanine) を使用して別の基板に分離することもできます。

ACカップリング コンデンサー

PCIeのリンクを配線するときの重要なポイントの1つは、ACカップリング コンデンサーの配置です。PCIeの設計経験がない場合、データシートを見てもこの点に気付かない可能性があります。ICベンダーが推奨するACカップリング コンデンサーの値はそれぞれ異なっています (例: XilinxのFPGAでは100nFが推奨されています)。これらは他のカップリング コンデンサーと同様に、リンクの両端に沿ったDCオフセットを除去し、同時にコンポーネント間でデータパルスの伝搬を可能にすることが目的です。

トレースとコネクタのインピーダンス

PCIeレーンの配線は、差動信号のベストプラクティス (差動インピーダンスが85Ωであることと、差動ペアネットクラス間の配線長の一致、および適切な間隔) に従う必要があります。長いトレース間に配置されるコネクタでは、PCIe準拠のコネクタでインピーダンスの大きな偏差 (最大15Ω) がよく発生するので注意してください。さらに重要な点は、この不一致がSパラメーターに影響 (具体的には復帰損失) に影響し、コネクタ、層の移行、または総合的な配線形式が許容されるものかどうかをテストにより判定する必要があることです。

仕上げとテスト

試作のテストやテストクーポンを行うとき、PCIe 5.0の仕様では作動ブレークアウト チャンネルをDUTからテスト用の設備に配線できます。PCIeチャンネルでの損失を評価するには、基板に同一のブレークアウト チャンネルを配置し、これを使用してチャンネルのSパラメーターを露出させます。その後で、チャンネルがPCIe 5.0の仕様を満たしているか、他の設計変更が必要かどうかを判定します。

PCIe 5.0互換のデバイスはまだ多くありませんが、設計においてはこれらの仕様に従うのが得策です。インテルのPCIe 5.0/DDR5互換のSapphire Rapids CPUは2021年に発売され、AMDも同等の製品を2022年に発売する予定です。幸い、PCIe 5.0の仕様は以前の世代のPCIeとも上位互換性があります。その後で、PCIe 6.0が登場するのも遠くないでしょう。

PCIe 5.0のレイアウトを設計し、基板上で信号を配線するには、Altium Designer®の高速設計ツールが必要です。あらゆるアプリケーション向けの高速基板の配線を設計し、大規模な量産の準備を行うために必要なツールが搭載されています。設計チームの他のメンバーと協力する必要があるときは、Altium 365®プラットフォームを使用して設計を共有し、レビジョンを追跡できるため、設計者は自宅からでも作業でき、これまでには考えられなかったような効率を実現できます。

ここで述べたのは、Altium 365でAltium Designerを使用して行える作業のごく一部にすぎません。より詳細な機能説明については、Altium 365の製品ページをご覧になるか、リソースページの情報をご覧ください。

今すぐAltium Designerの無償評価版をリクエストして、世界最高のPCB設計ソリューションをお試しください!ご不明な点などございましたら、お問合せフォームにご入力ください。