ピン、パート、差動ペアスワップによる配線の簡素化

PDFをダウンロードしてオンラインで学ぶ

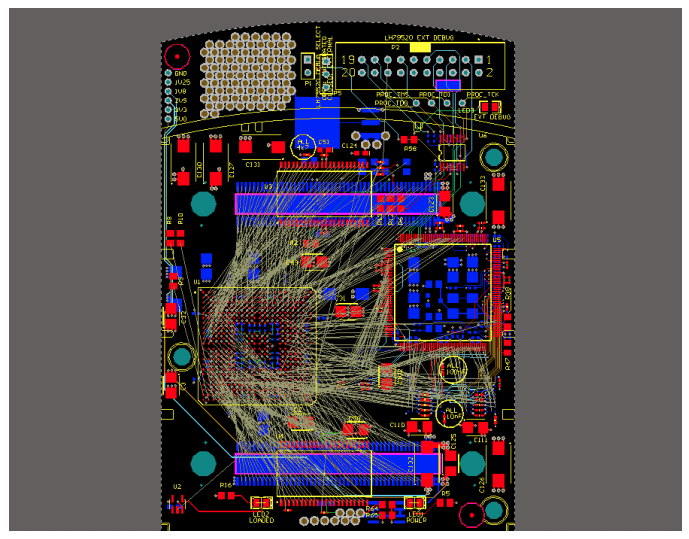

PCBデザインで部品を配置するとき、その配置のためにコネクションが互いに交差することは珍しくありません。コネクションの多少の交差は、他のレイヤーへのビアや、少し長い配線を使用して対処できますが、次の図に示すような多くの交差がある場合、配線は非常に難しく、時間を要するものとなります。

多くの交差を含む、より複雑な配線の場合、PCB設計者は一般にデバイスピンやサブパートをスワップして、コネクションの交差数を減らします。ピンやパートスワップによりPCBでの交差は解消できますが、このような変更は回路図に反映させる必要があります。このホワイトペーパーでは、ピン、サブパート、差動ペアスワップによりコネクションの交差を減らして最適の配線を実現しながら、回路図とPCB間のデザインの同期を維持する方法につ いて説明します。

はじめに

コンポーネントの最適な配置により、コネクションラインの交差を最小化するには、多くの作業が必要です。しかし、交差を完全に避けることは不可能です。多くのコネクションの交差が存在すると、PCBの配線は非常に難しくなり、完了には多大な時間を要します。PCB設計者は、電気的に可能ならば、ネット割り当てをデバイスの特定のピンから、別の使用可能なデバイスのピンにスワップすることが一般的です。同様に、共通パッケージ内のサブパートをスワップして、コネクションの交差を減らすこともできます。

ピンスワップは、2つの異なるピンのネットが、デザインの電気的な機能に悪影響を及ぼさないでスワップできます。基本的な例は、抵抗の2つのピンです。抵抗のピンには固有の極性が存在しないため、交差を解消するためにピンを自由にスワップでき、機能は変化しません。

別の実践的な例はピン数の多いコネクタで、各ピンに信号割り当ての厳格な要件が存在しない場合です。コネクタの多くのピンを柔軟にスワップできるため、いくつかのコネクションの交差を解消できる可能性があります。最もピンスワップの対象となるコンポーネントタイプはFPGAデバイスでしょう。 これらのデバイスにはユーザー定義可能なI/Oピンがあり、該当する電圧バンク内で、必要に応じてピンを自由に再割り当てできます。

サブパートのスワップでは、共通のパッケージ内に存在する類似パートがスワップされます。例えば、LM6154 QuadオペアンプICは単一のパッケ ージ内に、4つの独立した、同一のオペアンプが含まれています。このため、オペアンプC(ピン8、9、10)をオペアンプA(ピン2、3、1)とスワップし、同じ機能を維持したままコネクションラインの交差を解消できます。サブパートのスワップは「ゲートスワップ」と呼ばれることがあります。これは、SN74S02N Quad NORゲートパッケージ内の4つの独立したゲートを自由にスワップできることを示しています。

デバイスのピンとサブパートのスワップは、コネクションの交差の総数を減らすため、非常に役立ちます。デバイスのピンまたはサブパートのスワップを正しく行うには、どのピンをスワップするか事前に定義する必要があります。さらに、PCBデザイン内でピンまたはパートスワップを行った後、その変更を反映するよう回路図を更新し、PCBレイアウトと回路図との同期を維持する必要があります。これらの同期を怠ると、致命的なエラーを引き起こす恐れがあります。

ピンとパートスワップ

ピンまたはパートスワップは、3つの一般的な手順で行われます。スワップデータの構成、ピンまたはパートスワップの実行、最後にスワップ内容で回路図を更新して同期する手順です。 (※続きはPDFをダウンロードしてください)

今すぐAltium Designerの無償評価版をリクエストして、世界最高のPCB設計ソリューションをお試しください!