最先端のPCB向け高速配線のガイドライン

今日の設計はますます高速化しつつあり、PCIe 5.0は32Gb/sに達し、PAM4ではシグナルインテグリティと速度が限界まで押し上げられています。正しい相互接続設計を行うには、信号が正しく受信されることを保証するために、高度なデバイスにおいてはノイズのマージンが小さく、電源の完全な安定性が要求され、その他、多くの条件が存在することを考慮する必要があります。

高度なデバイスは低い信号レベルで動作するため、高速配線のガイドラインでは相互接続の全体を通して、インピーダンスの不連続から発生する信号の損失、歪み、反射を抑止することが焦点となります。超高速な信号処理、特にマルチレベル信号処理を使用する場合には、ここで紹介する高速設計ガイドラインの全てを十分に検討し、実践に移す必要があります。

高速配線の重要なガイドライン

今日の信号速度はナノ秒未満の世界に突入しつつあり、特に新しい世代のPCIeや高速ネットワーク機器を対応するため、設計者はいくつかの基本的な高速PCB配線のガイドラインに留意する必要があります。新しいデバイスが出現するたびに、以前の機器の速度限界が突破されていく状況においては、アプリケーションにおいてこれらのガイドラインのいくつかを満たすだけでなく、全てのガイドラインに注意する必要があるでしょう。

インピーダンス配線とパワーインテグリティをコントロールするスタックアップ

スタックアップはパワーインテグリティと同様に、シグナルインテグリティのためにも重要です。同様に、信号の帯域幅が数十GHzに達すると、特にマルチレベル信号処理方針を使用する場合は (例えば、PAM4で400Gのネットワークを実現する場合)、正しい終端とマッチングを保証するためにインピーダンスのコントロールが必要になります。また、リンギングを最小に抑える(すなわち、過渡応答を大幅に弱める)ためトレースを適切なサイズにし、同時にインピーダンスを一定に保つことも必要です。これには、スタックアップ技術と相互接続の細心な設計が必要です。

作動ペア配線と配線長の一致

シグナルインテグリティにおいて同相モードノイズは大きな問題となるため、インピーダンスのコントロールされた配線の一部として、作動ペアの全長にわたって十分なカップリングを確保する必要があります。これには、作動ペアの全長における位相の一致も必要です。このカップリングされたリジョンは、可能ならレシーバーまで直接延ばし、カップリングされていないリジョンは全長を一致させ、相互接続内のドライバーに閉じ込める必要があります。これによって同相モードのノイズが完全に位相一致し、レシーバーで完全に抑制されることを保証できます。

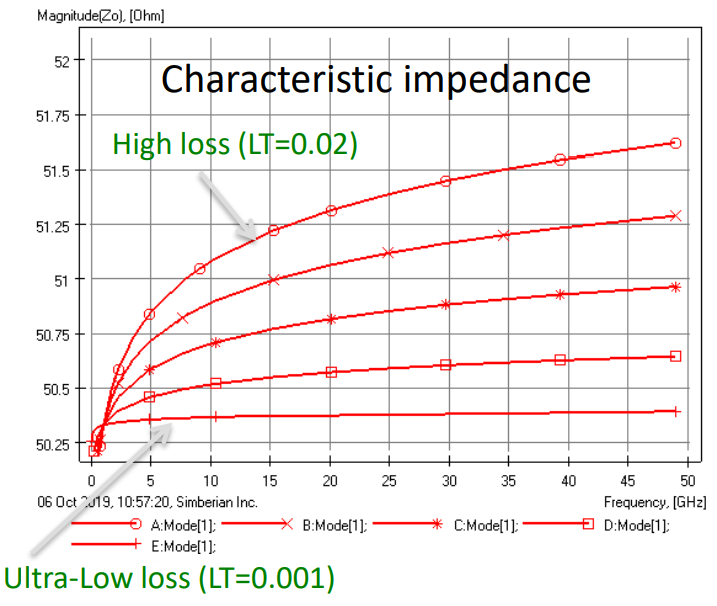

正しい基板材質の選択

立ち上がり時間が短くなると、損失タンジェントが小さく分散が平坦な材質の基板を探す必要があります。分散は、相互接続の全長にわたってインピーダンスと伝搬定数の継続的な変化を引き起こすため、非常に重要となります。まず、電磁気パルス (デジタル信号) が伝搬されるとき、分散によって拡散が引き起こされます。次に、強い分散が存在すると、信号の立ち上がりエッジで見られるインピーダンスと、信号の立ち下がりエッジで見られるインピーダンスとが一致しないため、大きな歪みが発生します。該当する帯域幅について絶縁定数が平坦であることを確認する必要がありますが、この帯域幅は12GbpsのPAM4では容易に30GHzの範囲に達します。

短いトレースとバックドリル加工

電力損失を最小に抑えるため、トレースは可能な限り短く配線します。パルスは分散によって引き延ばされるため、分散が問題となる場合に、これによってパルスの歪みを最小限に抑えることができます。トレース上のビアも、正確なインピーダンスに設計されていないとインピーダンスの不連続を引き起こす可能性があるため、数は最小限にします。相互接続上に存在するビアは必ずバックドリル加工します。ビアにスタブが残っていると、さらにインピーダンスの不連続が増え、信号が反射する可能性が生じます。さらに、これらのスタブは高速または高周波数で共鳴し、アンテナとして作用して、近くの相互接続にノイズを紛れ込ませる恐れがあります。

高速と高データ速度との比較: マルチレベル信号処理とファイバー

単純なOOK変調またはNRZ変調の信号では、信号レベルは実質的に2つで、バイナリのON/OFFの状態を定義します。実際には、作動相互接続のドライバーにより供給される信号の立ち上がり/立ち下がり時間によってデータ速度が制限されます。より高いデータ速度に移行すると、立ち上がり/立ち下がり時間は限界まで短縮され、32、56、112Gbpsではps単位にまで減少します。

これにより、許容されるジッターも非常に低レベルとなり、電力バスのリップルが、大電力を消費するICの出力に伝搬されないことを保証するため、電力の十分な安定性が必要となります。PDNのリップルにより、駆動されるICに約100ps/mVのジッターが誘発されるのは一般的なことです。このため、PDN上のリップルを1.2Vのデバイスについて約2% (ピークトゥピーク電圧で約30mVの変動に相当します) に低下させるには、PDNのインピーダンスをmΩ未満のレベルにする必要があります。ジッターは、マルチレベル信号処理を使用するPCBに適切な、約1psまたはそれ未満のレベルに抑える必要があります。

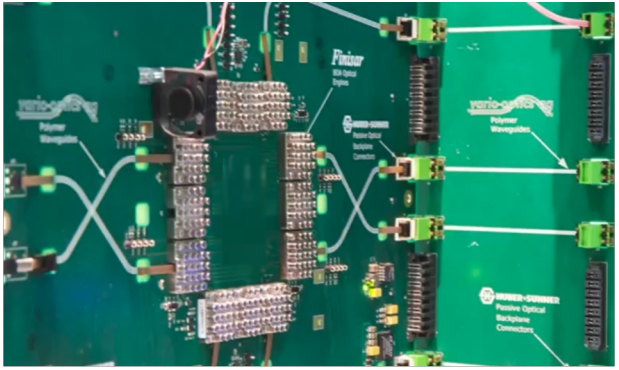

このような低い信号レベルで、データ速度を上げるために、より多くのチャンネルを並列に配線して帯域幅密度を上げる必要があります。ネットワーク機器では、超高速の光ファイバー ネットワーク機器で、より多くの並列なTxおよびRx多重化チャンネルと接続するため、作動信号処理が引き続き使用されるでしょう。光学系はPCBに直接取り付けられ、高速のフォトダイオードと帯域幅の高いVCSELを使用してシステムチップと接続されます。

新しいネットワーク機器や、他の高度なアプリケーションの要求を満たすため、設計者はどのようにしてデータ速度をさらに引き上げればいいでしょうか? 実際のところ、PCBレベルで光学機器と電子機器との集約が始まりつつあり、最終的にはICレベルで行われるようになるでしょう。主要なICメーカーは既にシリコン光量子ICのサプライチェーンを作り上げ、それらの新製品についてある程度の標準化を行うため結集しつつあります。これにより、シグナルインテグリティの課題の多くは緩和され、PCBコミュニティでは設計の制約のいくつかが緩められるでしょうが、設計者は高度な製品の作成方法を再考する必要に迫られるでしょう。

基板設計CADのAltium Designer®に搭載されている包括的な配線ツールは、ここで示したPCBの高速配線のガイドラインを定義、実装、その他多くの作業を行うために理想的です。高速配線の重要なガイドラインを設計ルールとして定義し、強力なシミュレーションツールでシグナルインテグリティを検査できます。これらのツールは単一のプラットフォームに統合されており、自分のワークフローへ迅速に組み入れることができます。

今すぐAltium Designerの無償評価版をダウンロードしてお試しください!業界最高のレイアウト、シミュレーション、データ管理ツールを1つのプログラムでご使用になれます。詳しくは今すぐアルティウムの専門家にお問い合わせください。