What's Different in HDI?

Defining Interconnect Density

When planning an HDI design, there are measures of performance or metrics for the HDI process. Like the triangle in Figure 1, these three vital chains of the HDI Process are elements of interconnection density.

FIGURE 1. HDI Design Metrics

Assembly Complexity

Two measures of the difficulty to assemble surface mounted components, Component Density (Cd), measured in parts per square inch (or per square centimeter.) and Assembly Density, (Ad), in leads per square inch or per square centimeter.

Component Packaging

The degree of sophistication of components, Component Complexity, (Cc), measured by its average leads (I/Os) per part. A second metric is component lead pitch.

Printed Wiring Board Density

The amount of density (or complexity) of a printed circuit, Wd, as measured by the average length of traces per square inch of that board, including all signal layers. The metric is inches per square inch. or cm per square centimeter. A second is the number of traces per linear inch or per linear cm. The PWB density was derived by assuming an average of three electrical nodes per net and that the component lead was a node of a net. The result was an equation that says the PWB density is times the square root of the parts per square inch times the average leads per part. ? is 2.5 for the high analog/discrete region, 3.0 for the analog/digital region and 3.5 for the digital/ASIC region:

PWB Density (Wd) = ? √ [Cd] x [Cc]

= ? √ [parts per sq. in.] x [ave.leads per part]

Where: p = Number of components (parts)

l = Number of leads for all the components

a = Area of the top surface of the board (square inches)

Packaging Technology Map

Figure 2 is what I call a Packaging Technology Map. The Packaging Technology Map was first displayed by Toshiba in January of 1991. [1].

A second valuable feature of the map is the area of upper-right. This is the “Region of Advanced Interconnections”. This is where it is necessary to have an HDI Structure. The dashed lines indicate the barrier or wall of HDI! Cross this and it now becomes cost effective to use HDI. Move too far and it becomes a necessity.

FIGURE 2. The through-hole (TH) wiring barrier as a function of a typical assembly

The packaging map is created by measuring an assembly size, number of components and the leads those components have. The components include both sides of an assembly as well as edge fingers or contacts. By the simple division of leads by parts and parts by area of the assembly, the X and Y-axis are known. Plotting the components per square inch (or components per square centimeter) against average leads per component on a log-log graph the PWB wiring density in inches per square inch (or centimeters per square centimeters) and Assembly Complexity (in leads per square inch or leads per square centimeter) can be calculated. The Assembly density is just the X-axis times the Y-axis.

Through-Hole Wiring Barrier

When the chart (Fig. 2) is used to analyze surface mount assemblies, three major zones show up on the packaging chart, which is why I call it a Map. The first is products with a high content of analog devices and discrete components. Typical products are camcorders, pagers and cellular telephones ( C-C’). They have the highest assembly complexity. Up to 300 to 400 leads per square inch (47 leads per square centimeter). The second group is products with a high degree of digital components and some mixed discretes. Notebook computers, desk tops, instruments, medical equipment and telecom routers are examples (A-A’). The last group has a highly integrated use of ICs. PCMCIA, flash memory, SiPs and other modules are typical of this group (B-B’). This group has the highest PWB wiring density of over 160 inches per square inch (25 centimeters per square centimeters). The Figure loosely shows the three regions.

When you look at the Figure, the Assembly Complexity lines cross the Wiring Density lines. At high discreet levels, less wiring is required for the amount of assembly density. At high ASIC (and low discreet) levels, much more wiring is required to connect the components. This makes assembly metrics like leads per square inch a good indicator, but not adequate to substitute for the PWB wiring density.

The General Process of PCB Design

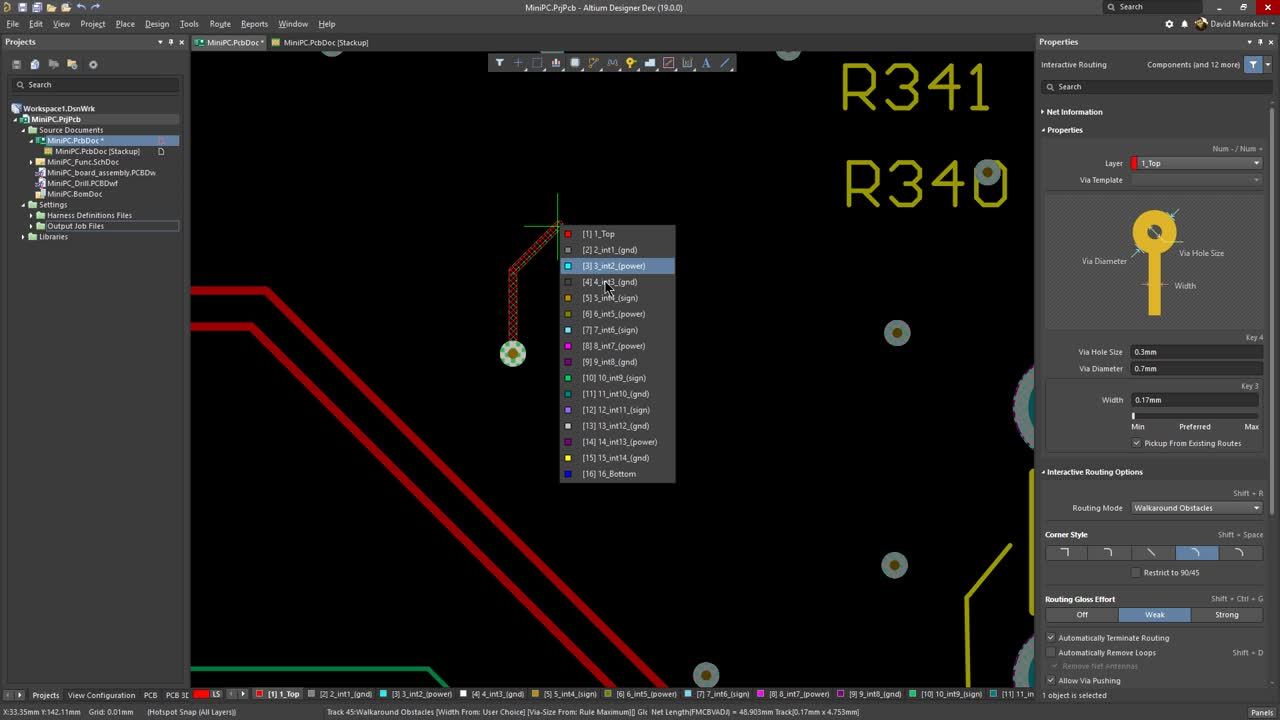

The process of PCB design utilizing HDI technology is shown in Figure 3. When designing with HDI technologies, the first step – [Plan Design] is the most important. Routing efficiencies for HDI is dependent on stackup, via architecture, parts placement, BGA fanout and design rules, as seen in Figure 4. But the entire HDI Value Delivery Chain must be taken into consideration, including fabrication yields, assembly considerations and in-circuit test. Working with your PWB fabricator and assembler is essential for a successful design.

FIGURE 3. A general overview of the PCB design and layout process

HDI Standards, Guidelines, Specifications and References

When approaching HDI design, the place to start is with the IPC Guidelines and Standards. Four apply specifically to HDI design, as seen in Figure 5.

- IPC/JPCA-2315: This is an overview of HDI and provides models for estimation design density.

- IPC-2226: This specification educates users in microvia formation, selection of wiring density, selection of design rules, interconnecting structures, and material characterization. It is intended to provide standards for use in the design of printed circuit boards utilizing microvia technologies. [2]

- IPC-4104: This standard identifies materials used for high-density interconnection structures. The IPC-4104 HDI Materials Specifications contain the slash sheets that define many of the thin materials used for HDI. The slash sheets of materials characteristics are divided into three main materials types: Dielectric Insulators (IN); Conductors (CD) and Conductor and Insulators (CI).

- IPC6016: This document covers the performance and qualification for high-density structures.

FIGURE 5. IPC standards and guidelines

What’s Different in HDI Design

Three (3) New Principles

There are three (3) new principles for HDI-microvia design that don’t exist in TH design:

Microvias must replace TH vias, not just used ‘”in addition to” TH vias.- Consider new layer stackups that allow the elimination of TH vias.

- Place microvias in such a way that they create channels and boulevards for improved routing. (see Table 1)

Microvias Replacing Through Holes (TH)

The main idea is that microvias replace or allow the removal of TH vias, thus allowing the routing density on inner layers to improve by 2X or 3X, using the space the TH vias used to occupy. This will allow fewer signal layers and fewer reference layers for those signal layers.

This principal is more profound than it first appears. This is because there are three dimensions on how the microvias are placed, see Figure 6):- The blind-vias can be “shifted or swung” in the X-Y or theta () angle to create more routing space

- The blind-vias can be placed on inner layer (3D) to further create more breakout spaces

- The center-to-center distance can be altered on inner layers to provide additional space for traces.

- If all of this is happening on or near the Primary Side, then there will be space created under the BGA on the Secondary Side for traces or more important, for discretes like decoupling capacitors.

FIGURE 6. Illustration of the benefits for routing by using blind vias

Layer Stackup Alternatives

If you study the first Principle and ask yourself, “What jobs do my vias do?”. The answer is that the most common via on a PWB are the vias to GND. “The second most common via?”, the answer is obvious, it’s the vias to PWR. Thus, moving the GND plane that usually is Layer-2 up to the surface provides the opportunity to eliminate all those vias to GND. In the same vein, moving the most used PWR plane up to Layer-2 will replace those THs with blind vias. These provide four (4) advantages over the conventional ‘microstrip’ stackup, as seen in Figure 7:

- There are no fine-lines to plate or etch on the surface.

- The surface can be an unbroken GND pour to reduce EMI and RFI (faraday cage)

- The closer Layer-2 (PWR) is to Layer-1 (GND) the more planar capacitance is available and the lower is the PDN planar inductance.

- The energy stored in the planar capacitance can be delivered to components with the lowest series inductance available, providing for the elimination of most of the decoupling capacitors.

Figure 7. shows some of the most common HDI stackups to reduce the number of TH vias. The three common HDI stackups are shown with the IPC-Type structures (I, II & III).

The possible dielectrics available between Layer-1 and Layer-2 can be conventional prepregs, laser-drillable prepregs, RCCs, reinforced RCCs or BC cores. These materials are described in Chapter 2 -HDI Materials. If the dielectric is thin, then it is practical to also utilize a ‘skip-via’ from Layer-1 to Layer-3, thus saving the cost of not having to utilize a IPC-Type III structure. Even if a thin dielectric is not employed, any dielectric thickness less than 0.005 inch (<0.125mm) will couple GND to PWR and provide a lower power supply (PS) impedance, as well as reducing PS resonances and noise.

FIGURE 7. Three alternative surface layer stackups compared to IPC-Type I, II & III structures

Placing blind vias to open larger boulevards

One useful HDI design technique is to use blind vias to open up more routing space on the inner layer. By using blind vias between the through-vias, the routing space effectively doubles on the inner layers,

FIGURE 8. Near-via-in-Pad definition and swinging the ViP to create channels for routing

allowing for more traces to connect pins on the inner rows of a BGA. As seen in Figure 6, for this 1.0 mm BGA, only two traces can escape between vias on the surface. But beneath the blind vias, now six traces can escape, increasing the routing by 30%. With this technique, one fourth the number of signal layers is required to connect a complex, high-I/O BGA. Blind vias are arranged to form boulevards either in a cross, L-shaped or diagonal formation. Which formation to use is driven by the power and ground pin assignment. This is why, for a FPGA, reprogramming the placement of power and ground pins can be so productive.

FIGURE 9. Blind vias can be used to form boulevards in inner layers allowing 30% more routing out of the BGA

The microvia used for BGA fanout was shown in Figure 9. The microvia can be placed outside the BGA land (inset), partially in/out of the land (partial vip) or completely in ‘the pad’ (vip)-see Figure 10.. If placing the via-in-pad, then the via should always be ‘off-center’ and not placed in the direct center of the land. This is to minimize any trapped air ‘voids’ during soldering. If the via is placed in the center of the BGA land, and it is not-filled, when the solder paste is applied on the land, and the BGA placed on the paste-land, during reflow, as the solder melts, the BGA ball drops and traps any air that may be there, much like a ‘cork in a bottle’. By placing the via ‘off-center’, the air has a chance to escape as the solder melts and flows into the microvia.

FIGURE 10. blind-via alternatives

FIGURE 11. Fancy 3D view of ‘swing-vias’ connecting to buried-vias and through-holes

Try out these HDI design basics today in Altium Designer®. Click the free trial. Or watch and see how Altium Designer supports HDI design with microvias support: