LIGNES DE TRANSMISSION ET TERMINAISONS DANS LES PCBÀ GRANDE VITESSE

QU’EST-CE QU’UNE LIGNE DE TRANSMISSION ?

Une ligne de transmission est une paire de conducteurs utilisés pour fournir de l'énergie sous la forme d'un champ électromagnétique. La plupart d'entre nous connaissent les câbles qui alimentent nos maisons en énergie pour notre éclairage et nos appareils. Dans le contexte de la conception des PCB, il s'agit d'un signal dans une couche de signal sur un plan ou entre deux plans.

LIGNES DE TRANSMISSION ET TERMINAISONS DANS LES PCB À GRANDE VITESSE

L'objectif de cette section est d'expliquer ce que sont les lignes de transmission ; ce qu’elles transportent, comment elles se comportent lorsqu’elles reçoivent des signaux de commutation et comment contrôler ces signaux de commutation avec des terminaisons de PCB pour obtenir la meilleure qualité de signal possible. Cette section inclut une liste de documents en guise de lecture complémentaire pouvant être utiles.

Une partie essentielle de cette section et des suivantes consiste à fournir des règles de conception valides avec la preuve de leur validité. Pour l'auteur, il est important que toutes les règles de conception soient accompagnées de leurs preuves et de leurs limites, le cas échéant.

QU’EST-CE QU’UNE LIGNE DE TRANSMISSION ?

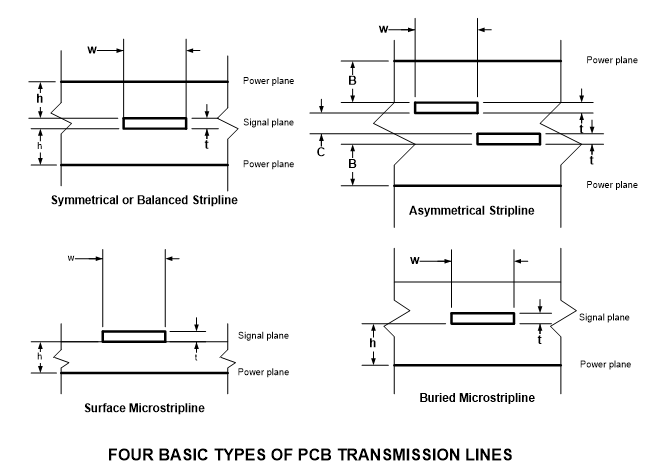

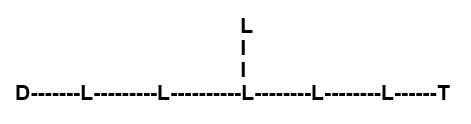

Au plus simple, une ligne de transmission est une paire de conducteurs utilisés pour fournir de l'énergie sous la forme d'un champ électromagnétique. La plupart d'entre nous connaissent les câbles qui alimentent nos maisons en énergie pour notre éclairage et nos appareils. Dans le contexte de la conception des PCB, il s'agit d'un signal dans une couche de signal sur un plan ou entre deux plans. Figure 1 : Les quatre types de lignes de transmission normalement utilisées dans les PCB. Les deux types principaux sont les lignes rubans (stripline) et les lignes micro-rubans (micro-stripline). Le premier type est une ligne de transmission entre deux plans. Le deuxième est une ligne de transmission sur un plan. Il est important de noter que le mot "masse" n'est pas utilisé pour décrire les plans. Le nom CC d'un plan n'a aucune importance en ce qui concerne les champs électromagnétiques.

Figure 1. Types de lignes de transmission de PCB

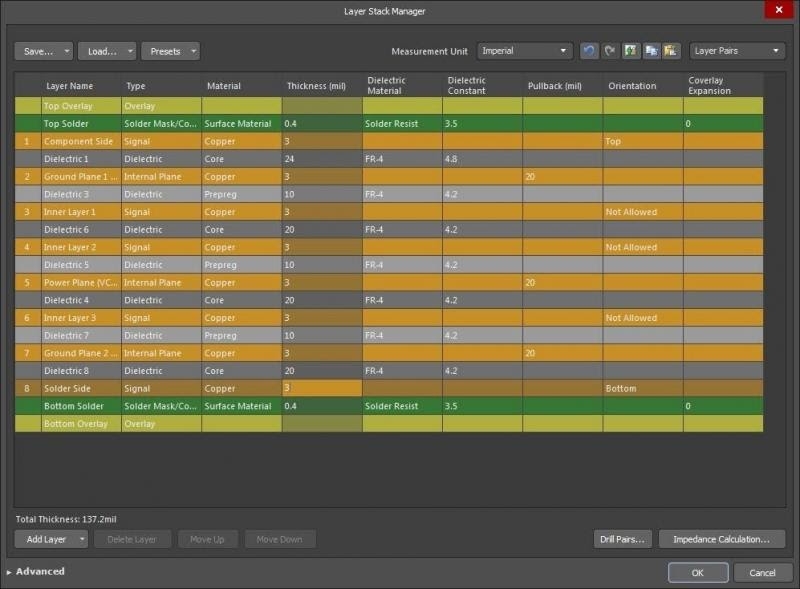

Diverses combinaisons de ces quatre configurations de lignes de transmission seront utilisées pour constituer un empilage de couches de PCB. Le contrôle de la diaphonie sera abordé dans la section suivante, concernant les signaux juxtaposés dans une couche de signaux ou superposés dans des couches de signaux adjacentes. De plus, le calcul de l'impédance caractéristique sera traité dans la section suivante.

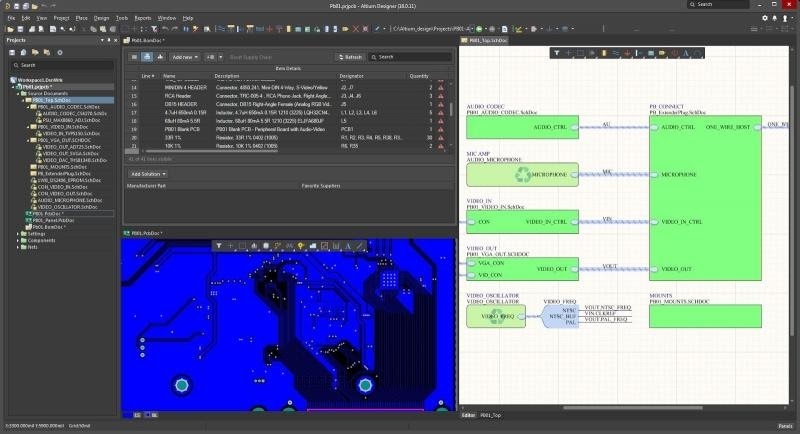

Travailler sur une ligne de transmission avec vos différentes impédances caractéristiques peut être un véritable casse-tête. Avec le bon logiciel de conception de PCB, vous devriez être capable de contrôler l'impédance et la diaphonie grâce à une stricte conformité aux règles de conception intelligentes, ainsi que la gestion des empilages de couches avec facilité et élégance. Altium Designer a gardé ces éléments à l'esprit pour concevoir son environnement de conception convivial.

Ligne de transmission dans l’ environnement de conception unifiée d'Altium Designer

QUE TRANSPORTE UNE LIGNE DE TRANSMISSION ?

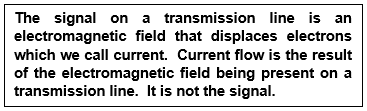

Afin de gérer correctement une ligne de transmission, il est important de savoir ce qu’elle transporte. Lorsque vous débutez en électronique, on vous enseigne la tension, le courant et le flux du courant comme signal. Malheureusement, cette vision de la signalisation est trop simpliste et si la gestion se concentre uniquement sur le flux du courant, la qualité des signaux risque d’être compromise.

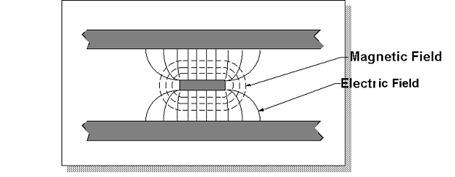

La plupart d'entre nous savent que les signaux électroniques se déplacent à la vitesse de la lumière, qui est de 186 000 miles ou 300 000 kilomètres par seconde ou presque, dans le vide. Le flux du courant, qui est le mouvement des électrons dans un conducteur de cuivre, se déplace à la vitesse d'environ 1 375 miles par heure ou 2 200 kilomètres par heure. Par conséquent, le signal ne peut pas être le flux du courant. Le champ électromagnétique est le signal. Figure 2 : Champ électromagnétique autour d'une ligne de transmission ruban. La ligne sort de la page entre deux plans (vue en bout).

Figure 2. Champ électromagnétique autour d'une ligne de transmission ruban

Notez qu'il y a deux types de champ dans ce dessin, les lignes de champ électrique entre la ligne de transmission et les deux plans, et les lignes de champ magnétique qui entourent la ligne de transmission. Le champ magnétique déplace les électrons dans la ligne de transmission que nous mesurons avec un ampèremètre et que nous appelons flux du courant. Un courant égal et opposé circule dans les deux plans que nous appelons souvent courant de retour. La répartition de ce courant de retour entre les deux plans dépend de la distance entre chaque plan et la ligne de transmission.

Savoir créer et gérer les champs électromagnétiques est la clé de la réussite dans l'électronique à haut débit.

CRÉER ET GÉRER DES CHAMPS MAGNÉTIQUES POUR CONCEVOIR DES PCB

Chaque signal électronique est destiné à délivrer une forme d'onde de tension à un récepteur. Pour ce faire, de l'énergie sous forme de champ électromagnétique est générée et envoyée sur une ligne de transmission jusqu’au récepteur. Figure 3 : Trajet de signal typique avec un driver, un récepteur et une ligne de transmission pour les relier.

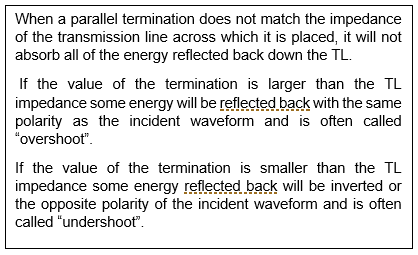

Lorsqu'il y a un décalage entre les lignes de transmission et les terminaisons des PCB ou les charges, des réflexions de différents types peuvent se produire, telle qu’une onde stationnaire. La gestion de ces scénarios impose du travail supplémentaire au concepteur du PCB, qui doit par exemple déterminer les coefficients de réflexion et la meilleure façon de prévenir les décalages.

Pour envoyer une forme d'onde de tension de la plus haute qualité au récepteur, il est important que le signal ne soit pas dégradé pendant son déplacement de la source au récepteur. Le plus souvent, la dégradation se traduit par une réflexion d'une partie du signal (énergie) à des impédances inadéquates. Idéalement, Zout = Zo = Zload, ce qui n'entraîne aucune réflexion. L'ingénierie de l'intégrité du signal s'efforce de répondre à cette exigence en concevant des empilages de circuits imprimés pour atteindre une impédance cible et en ajoutant des terminaisons de PCB pour réduire les décalages.

Figure 3. Cheminement typique du signal avec source, charge et ligne de transmission

Terminaisons

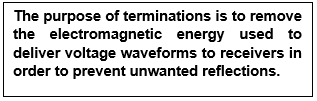

Lorsque l'énergie électromagnétique envoyée sur une ligne de transmission a fourni la forme d'onde de tension sur le récepteur, elle doit être retirée du système, sinon elle se réfléchit et provoque des transitoires indésirables qui peuvent entraîner un faux déclenchement des charges le long de la ligne ou détruire une entrée si les réflexions sont trop importantes. Le but des terminaisons de PCB est de supprimer cette énergie lorsque la forme d'onde de tension a été délivrée.

Il existe deux types de terminaisons de PCB. Les terminaisons sérielles et parallèles. Figure 4 : types de terminaisons utilisables et comment ces terminaisons se connectent à une ligne de transmission. Les terminaisons en série se connectent dans le nœud à la sortie du driver. L’extraction de l'énergie électromagnétique par la terminaison sur la ligne de transmission est expliquée dans la section suivante. Des terminaisons parallèles sont fixées à l'extrémité côté driver d'une ligne de transmission pour extraire l'énergie électromagnétique après son arrivée au récepteur.

Figure 4. Types de terminaisons.

Figure 4 : Notez qu'il y a quatre terminaisons placées à l'extrémité de la ligne de transmission proche du récepteur. Les terminaisons parallèles peuvent être mises en œuvre de diverses façons. Les avantages de chaque type seront décrits plus tard. Il n'y a qu'une seule terminaison située près du driver. Cette terminaison est sérielle. La section suivante décrit la méthode de contrôle des réflexions.

Les quatre options des terminaisons parallèles sont les suivantes : CA, diode, Thevenin et résistance unique pour une tension de terminaison.

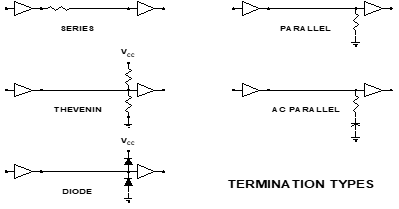

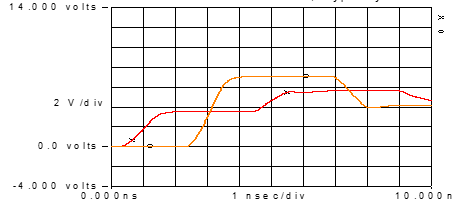

Les terminaisons CA trouvent leur origine à l'époque du TTL, lorsque le temps de montée est devenu suffisamment court pour nécessiter une terminaison parallèle au niveau du récepteur. Comme le TTL ne pouvait pas supporter la charge continue d'une terminaison de 50 ohms, un condensateur a été utilisé pour connecter la terminaison à la ligne de transmission, lui permettant d'absorber l'énergie du front de commutation rapide, tout en restant déconnecté en régime permanent. Cela a fonctionné tant que le rapport entre le temps de montée et la fréquence d'horloge était très important. À mesure que la vitesse de l'horloge augmentait, la dégradation indiquée à la Figure 5 a entraîné une dégradation du signal au point qu’il en devenait utilisable. La forme d'onde rouge est le signal qui sort du driver. La forme d'onde orange est le signal qui arrive au récepteur. Il est clair que cette méthode de terminaison parallèle sur une ligne de transmission n’est pas satisfaisante et qu'elle ne devrait jamais être utilisée.

Figure 4. Horloge avec terminaison de PCB CA à 66 MHz

Les terminaisons à diodes sont apparues lorsque les sur-dépassements, des réflexions qui s'élèvent au-dessus de Vdd ou s'étendent sous la masse, ont dépassé la tension d'entrée nominale des récepteurs. Comme on le verra, ce problème peut être évité en utilisant de simples terminaisons parallèles ou en sérielles. La terminaison à diode est un moyen très coûteux de contrôler les sur-dépassements et ne devrait jamais être utilisée.

Mais cette règle a son exception. Le bus PCI nécessite des terminaisons sérielles sur les sorties de tous les drivers. Les ingénieurs qui ont conçu les cartes d'extension pour les PC qui n'ont pas compris cela, ont omis d’ajouter des résistances de terminaison sérielles pour faire des économies. Lorsque ces cartes étaient branchées sur la carte mère d'un PC, il y avait souvent une défaillance due à un sur-dépassement. Le consortium responsable de la norme de bus PCI n'a pas pu empêcher que cela se produise et a imposé une exigence dans le cahier des charges selon laquelle toutes les entrées doivent être dotées de diodes pour être conformes à la norme PCI ; ce qui a permis de résoudre le problème.

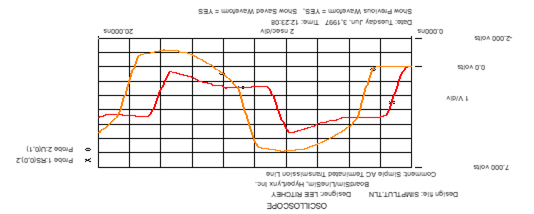

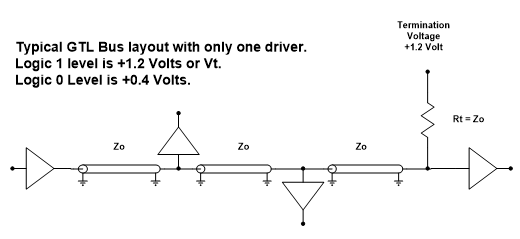

Les terminaisons parallèles résistives sont le moyen le plus simple pour terminer une ligne de transmission. Figure 5 : Bus GTL avec terminaison parallèle. Notez que la résistance de terminaison se connecte à une tension d’extrémité, généralement appelée Vtt, qui est une alimentation électrique distincte de Vdd. Cela signifie qu'un système utilisant des terminaisons parallèles nécessite deux unités d’alimentations capables de fournir des transitoires de commutation très rapides. Lorsqu'un système comporte de nombreuses lignes de transmission qui doivent être terminées en parallèle, ce coût supplémentaire en vaut la peine. Lorsque seules quelques lignes doivent être terminées en parallèle, comme les lignes d'horloge dans certaines configurations DDR, ce coût supplémentaire peut être une charge. Dans ce cas, une terminaison de Thevenin est utile.

Figure 5. Ligne de transmission GTL à terminaison parallèle

Les terminaisons parallèles Thevenin constituent une méthode qui permet de créer l'équivalent des Vtt et Rt nécessaires pour terminer en parallèle une ligne de transmission sans avoir besoin d'une alimentation électrique séparée pour les Vtt. Figure 6 : Méthode de calcul des valeurs des résistances pour un réseau de terminaison Thevenin ainsi qu'un exemple de calcul.

Figure 6. Méthode de calcul des valeurs des résistances terminales de Thevenin

Fonctionnement des terminaisons sérielles

Les lignes de transmission à terminaison sérielle sont la principale méthode de connexion des dispositifs logiques CMOS. Il est essentiel de comprendre le fonctionnement de ces lignes de transmission pour s'assurer que les signaux sont correctement transmis à chaque récepteur. Ce fonctionnement n'est pas intuitif et déroute certains d'entre nous jusqu'à ce qu'il soit expliqué. Ce bref exposé vise à dissiper une partie de la confusion.

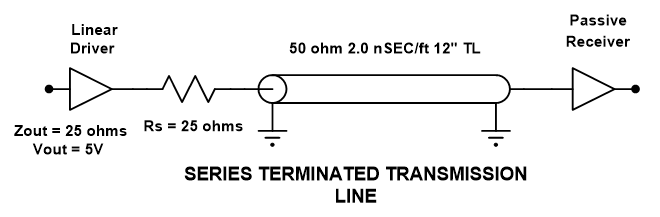

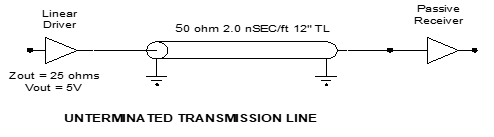

Figure 7 : Un driver CMOS 5V typique avec une ligne de transmission de 50 ohms connectée à un récepteur CMOS passif. Cela signifie qu'il répond simplement à la forme d'onde de tension présentée sur l'entrée. (Pour les besoins de cette explication, les récepteurs CMOS ressemblent à de très petits condensateurs qui peuvent être considérés comme des circuits ouverts). Dans cet exemple, la ligne fait 12 pouces ou environ 30 cm de long. Dans un PCB, l'énergie se déplace à une vitesse d'environ six pouces par nanoseconde. Cette ligne a donc une longueur d’environ deux nanosecondes.

Figure 7. Circuit CMOS 5V à terminaison de PCB sérielle typique

Figure 8 : Circuit équivalent pour une ligne de transmission semblable à celle de la Figure 7.

Figure 8. Un circuit équivalent pour la ligne de transmission dans la Figure 7.

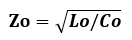

Remarquez la capacitance, la résistance et l’inductance réparties sur la longueur de la ligne de transmission. Ces éléments appelés parasites déterminent le comportement d'une ligne de transmission, le rapport entre l'inductance par unité de longueur et la capacitance par unité de longueur déterminant l'impédance caractéristique de la ligne comme indiquée dans l'équation 2.

Lo est l'inductance par unité de longueur et Co est la capacitance par unité de longueur. Ces deux variables sont déterminées pour un type particulier de ligne de transmission à l'aide d'un outil spécifique, tel qu'un solveur de champ 2D. De nombreux solveurs de champ sont disponibles dans le cadre des outils d'intégrité des signaux.

Dans presque tous les cas, la valeur R est si faible par rapport à celle de L et C qu'elle peut être ignorée. Tant que les fréquences concernées ne dépassent pas un GHz, cette hypothèse reste raisonnable.

Équation 2. Impédance en fonction de la capacitance et de l'inductance distribuées

Lorsque le driver de la Figure 7 souhaite faire passer le niveau logique sur la ligne de transmission de 0 logique à 1 logique, il doit charger la capacité parasite distribuée de la ligne de transmission. C'est l'énergie primaire consommée par les circuits logiques CMOS. Lorsque le même driver souhaite faire passer le niveau logique de 1 logique à 0 logique, il doit supprimer cette charge.

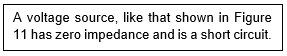

Conseil : Lorsqu'un signal est envoyé sur un fil ou une ligne de transmission, cette énergie prend la forme d’un champ électromagnétique. Cette énergie suit le chemin et sera indéfiniment réfléchie à ses extrémités, à moins qu'elle ne soit absorbée par une résistance terminale ou qu'elle ne se perde lentement dans la résistance du conducteur. Si les extrémités du chemin sont des circuits ouverts, l'énergie réfléchie sera de même polarité que l'énergie incidente. Si les extrémités du chemin sont des courts-circuits, l'énergie réfléchie sera inversée.

Comment une charge sur une ligne logique permet de la passer de 0 à 1

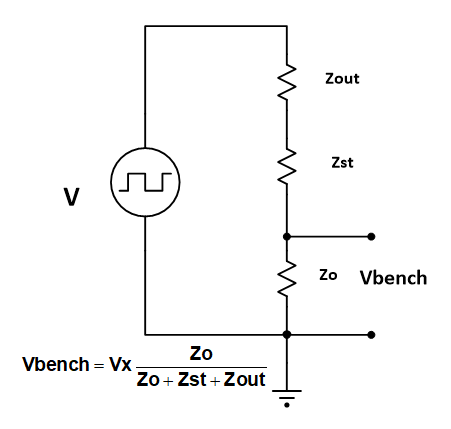

Figure 9 : Circuit équivalent de la Figure 7 au moment où le driver commence à déplacer la ligne logique de 0 à 1. Notez qu'un diviseur de tension est formé par la combinaison de l'impédance de sortie du driver et de la terminaison sérielle dans la partie supérieure, et de l'impédance de la ligne de transmission dans la partie inférieure. Lorsque la terminaison sérielle a été correctement choisie, la combinaison de Zout et Zst sera identique à Zo. Dans cet exemple, les deux seront de 50 ohms et la tension à l'entrée de la ligne de transmission sera donc de V/2.

Figure 9. Circuit équivalent de la Figure 7 quand une transition de 0 à 1 débute

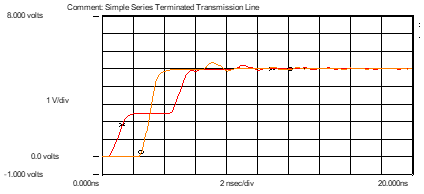

Figure 10 : Formes d'onde de tension à l'entrée de la ligne de transmission et à l'entrée du récepteur au fur et à mesure que le temps passe. La forme d'onde rouge est l'entrée de la ligne de transmission et la forme d'onde orange est l'entrée du récepteur à la fin de la ligne de transmission. Remarquez que le niveau de tension immédiatement après la transition de 0 à 1 ne représente que la moitié de Vdd ou une demi-taille. Cela est dû au diviseur de tension illustré à la Figure 9. Ce niveau de tension est souvent appelé tension de "banc".

Sur la ligne de transmission, l'énergie prend la forme d'un champ électromagnétique (EM) avec une composante de tension égale à V/2. Cette énergie charge la capacitance parasite de la ligne de transmission à un niveau de tension V/2 lorsque le champ se déplace sur la ligne de transmission.

Après deux nanosecondes (la longueur électrique de la ligne de transmission), la ligne a été complètement chargée à V/2 et le champ électromagnétique rencontre un circuit ouvert au niveau du récepteur. Lorsqu'un tel champ rencontre un circuit ouvert, aucune partie de l'énergie du champ n'est absorbée et elle est réfléchie avec la même ampleur que lorsqu'elle est sortie.

Au moment de la réflexion totale, le niveau de tension à l'extrémité de la ligne est de V/2. Comme l'amplitude de tension du champ électromagnétique est de V/2 après la réflexion totale, l'amplitude sera de V. Notez que la forme d'onde orange a une amplitude de V dès que le champ EM arrive en bout de ligne. Au retour, la capacité parasite de la ligne de transmission est chargée jusqu'à V. Lorsque le champ électromagnétique revient au driver, il rencontre le circuit équivalent illustré à la Figure 11.

Figure 10. Formes d'onde de la tension aux deux extrémités de la ligne de transmission dans la Figure 7.

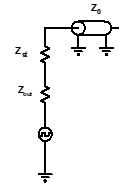

Figure 11. Circuit équivalent du driver de la Figure 7 vu par le champ électromagnétique réfléchi

Puisque la somme de Zout et Zst est de 50 ohms, et la source de tension est un court-circuit. Ensemble, ils constituent une terminaison parallèle qui a la même valeur que l'impédance caractéristique de la ligne. Ainsi, toute l'énergie du champ électromagnétique est absorbée et le niveau de tension sur la ligne de transmission se stabilise à 5 volts, soit 1 logique idéal pour ce circuit.

Passer de 1 logique à 0 logique

Lorsque le circuit de la Figure 8 passe de 1 à 0 logique, le driver doit éliminer la charge placée sur la capacité de la ligne pour passer de 0 à 1 logique. Pour ce faire, le niveau du driver passe de 5V à 0V en interne. Comme pour la transition de 0 logique à 1 logique, le circuit équivalent correspond à la Figure 9, mais maintenant, la ligne est à 5V et l'impédance de sortie et la résistance de terminaison sérielle sont connectées à 0V. Le diviseur de tension a le même effet qu’auparavant.

Par conséquent, la tension de ligne est déplacée à V/2 et la charge est retirée de la capacitance de la ligne à ce niveau lorsque l'énergie se déplace le long de la ligne. (Le niveau de tension de ces transitions est de -V/2.) Lorsque le champ électromagnétique arrive à l'extrémité de la ligne de transmission deux nanosecondes plus tard, il rencontre un circuit ouvert, puis il est réfléchi sur la ligne. Le résultat après que la réflexion ait eu lieu est que la ligne est maintenant à 0V. Deux nanosecondes plus tard, le champ EM revient au driver, rencontre le circuit illustré à la Figure 5, puis est absorbé. La forme d'onde résultante est illustrée à la Figure 12.

Figure 12. Formes d'onde de tension aux deux extrémités de la ligne de transmission après commutation de 1 à 0

Notez que la forme d'onde de tension au niveau du récepteur (orange) est un signal logique d'onde carrée qui constitue l’objectif du chemin du signal. Cette méthode de signalisation est connue sous le nom de commutation par "onde réfléchie" car le niveau logique correct est créé par l'onde réfléchie lorsqu'elle fait son aller-retour le long de la ligne de transmission. Cette méthode de signalisation logique à haut débit consomme le moins d'énergie, car le courant n'est prélevé sur le réseau électrique que lorsque la ligne est chargée. Lorsque la ligne est entièrement chargée à 1 logique, l’appel de courant passe à zéro.

Cette méthode de commutation est employée avec le bus PCI incorporé dans la plupart des ordinateurs personnels.

Notez également que la forme d'onde de la tension à la sortie du driver est dans un état logique indéterminé pendant une durée égale au délai aller-retour sur la ligne de transmission à chaque commutation. Si les charges sont placées sur le long de la ligne de transmission, comme c'est le cas avec le bus PCI, elles n’aboutissent pas à un état de confirmation des données (“data good”) avant que l'onde réfléchie ne passe devant elles au retour. Par conséquent, la synchronisation des données sur ces entrées doit être retardée jusqu'à ce que les données soient bonnes sur toutes les entrées. C'est ainsi que les données sont synchronisées sur le bus PCI et d'autres protocoles de bus qui reposent sur la commutation par ondes réfléchies.

Editeur d'impédance dans l'éditeur de règles et de contraintes d'Altium Designer

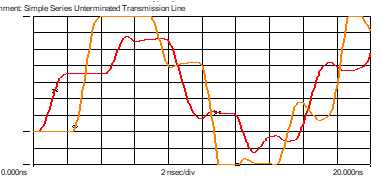

Que se passe-t-il lorsque l'impédance du driver ne correspond pas à l'impédance de ligne ?

Le circuit illustré à la Figure 13 est le même que celui illustré à la Figure 7, sauf que la terminaison sérielle n'a pas été insérée en série avec la sortie.

Figure 13. Ligne de transmission CMOS 5V non terminée

La Figure 14 montre la forme d'onde de commutation pour la transition de 0 logique à 1 logique. Remarquez que la tension du banc est largement supérieure à V/2. En fait, il s'agit de 2V/3 ou 2/3 du total de 5 volts ou 3,33V. Pourquoi ? Si vous vous référez au diviseur de tension de la Figure 3, dans cet exemple, la résistance supérieure est de 25 ohms, ou Zout du driver, et la résistance inférieure ou impédance caractéristique est de 50 ohms produisant le niveau de tension 2/3.

Le champ EM charge la capacitance de la ligne à cette valeur comme avant. Lorsque le champ EM arrive au récepteur deux nanosecondes après avoir été généré, il est réfléchi, doublant la tension à 6,66V. Comme auparavant, le champ EM charge la capacitance de la ligne jusqu'à 6,66V. Deux nanosecondes plus tard, le champ EM revient au driver, et rencontre une terminaison, similaire celle illustrée dans la Figure 5. Toutefois, la terminaison parallèle n'est pas de 50 ohms. Elle est de 25 ohms. Deux événements interviennent alors. Premièrement, le diviseur de tension est cette fois de 50 ohms en haut et de 25 ohms en bas comme indiqué dans la Figure 15. La valeur du terminateur sérielle étant de zéro ohms, donc la tension est divisée vers le bas. Deuxièmement, toute l'énergie ne sera pas absorbée.

Lorsqu'un champ EM rencontre une terminaison parallèle de valeur inférieure à la TL, l'énergie réfléchie sera de polarité opposée à la forme d'onde incidente. Cela ne peut pas être vu par le driver. Deux nanosecondes plus tard, l'énergie arrive au récepteur et, comme on peut le voir, elle est inversée ou négative.

Comme avant, la quantité d'énergie doublera le niveau de tension au niveau du récepteur et retournera vers le driver. Lorsqu'elle arrive au driver, une partie est absorbée et le reste est réfléchie inversée. Cela se poursuit jusqu'à ce que toute l'énergie soit absorbée dans l'impédance de sortie du driver et que le niveau logique se stabilise à 5V. Comme l’illustre la Figure 16.

Figure 14. Commutation de la forme d'onde pour une ligne de transmission CMOS non terminée

Figure 15. Circuit équivalent de la Figure 13, Zst = 0

Figure 16. Commutation de la forme d'onde pour une ligne de transmission CMOS non terminée

La forme d'onde de la Figure 16 pose deux problèmes. Tout d'abord, le voltage dépasse le Vdd de 1,66 volt. Cet excès de tension peut provoquer des défaillances logiques ou endommager le récepteur. Ensuite, lorsque le signal revient au driver et est inversé, il fait chuter le 1 logique du récepteur en dessous de 4 volts. Cela réduit la logique à un niveau qui pourrait entraîner une défaillance de la logique. Ces deux problèmes doivent être évités. C'est pourquoi une terminaison sérielle est ajoutée à un circuit comme celui-ci.

La Figure 17 présente la forme d’onde lorsque le signal passe à 0 logique. Comme vous pouvez le voir, les violations de même niveau se produisent dans cet état logique.

L'échelle est de 1 volt par division, la ligne inférieure étant à -1 V et la ligne supérieure à 8 V.

Figure 17. Une autre commutation de la forme d'onde pour une ligne de transmission CMOS non terminée

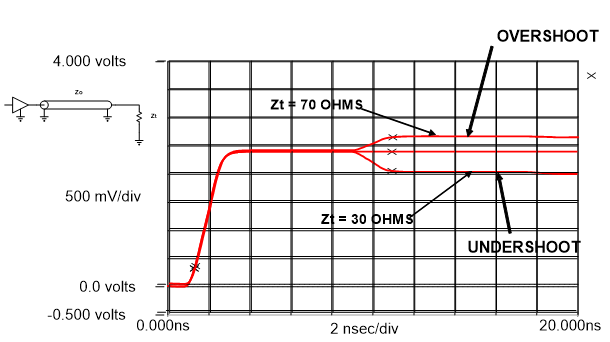

Sur-dépassement et sous-dépassement

Les termes sur-dépassement et sous-dépassement décrivent les excursions indésirables des formes d'onde du signal dues aux réflexions provoquées par les changements d'impédance. La Figure 18 illustre une ligne de transmission à terminaison parallèle de 50 ohms avec trois valeurs différentes de résistance de terminaison. Les formes d'onde indiquées sont mesurées à la sortie du driver. Lorsqu'une ligne de transmission est parfaitement terminée dans son impédance caractéristique, dans ce cas 50 ohms, toute l'énergie est absorbée par le terminateur lorsqu'elle arrive au récepteur et aucune énergie n'est renvoyée vers le driver. Comme le montre la forme d’onde centrale dans la Figure 18.

Figure 18. Ligne de transmission à terminaison parallèle

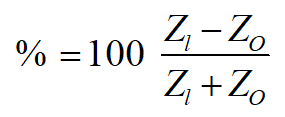

Lorsque la valeur du terminateur a été réglée sur 70 ohms, la ligne n'était plus parfaitement terminée et une partie de l'énergie a été renvoyée au driver. L'équation 3 est souvent appelée l'équation de réflexion. Elle sert à calculer la quantité de réflexion qui se produira en cas de décalage d'impédance. Dans l'équation, Zl est l'impédance amont et Zo est l'impédance aval. Dans ce cas, l'impédance amont est l'impédance de ligne, 50 ohms, et l'impédance aval est la résistance de terminaison. Lorsque la résistance terminale est à 70 ohms, l'équation prédit une réflexion de 16% de la tension incidente, avec une polarité positive, s'ajoutant à la tension incidente comme on peut le voir sur la Figure 18, causant un sur-dépassement.

Lorsque la valeur du terminateur est réglée sur 30 ohms, la ligne n'est plus parfaitement terminée et une partie de l'énergie est renvoyée au driver. En utilisant l'équation 3, la valeur réfléchie est de 25%, mais la valeur est négative, au détriment de la valeur de l'incident. On parle alors de sous-dépassement.

Équation 3. Équation de réflexion

Lorsque les tensions logiques étaient de l'ordre de 5 volts, le sur-dépassement devenait souvent si important qu'il causait des défaillances logiques ou même des dommages aux circuits. C'est pourquoi l'accent a toujours été mis sur la nécessité d'éviter les dépassements excessifs. C'est la raison des diodes sur les entrées. Comme les niveaux logiques ont continué à baisser, la probabilité d'une panne a diminué. En même temps que les niveaux logiques ont baissé, la marge de bruit a également diminué. Par conséquent les défaillances logiques dues au bruit couplé deviennent un problème important. Par conséquent, on s’efforcera toujours d'éviter les sous-dépassements avec la plupart des familles logiques actuelles.

Déterminer les valeurs des résistances de terminaison

Comme indiqué précédemment, il existe deux types de terminaisons de PCB : sérielle et parallèle. Pour une terminaison parallèle, la valeur est celle de l'impédance caractéristique du circuit de terminaison ou de la ligne de transmission qui est terminée. Déterminer les valeurs des résistances de terminaison sérielle n'est pas si simple. La résistance de terminaison sérielle sera ajoutée à l'impédance de la ligne de transmission lorsqu'elle est combinée à l'impédance de sortie du driver. Par conséquent : Zst = Zo – Zout. Comment obtenir l'impédance caractéristique de sortie du driver ? Il serait bon que ces informations soient imprimées dans la fiche technique du composant. Malheureusement, c'est rarement le cas. Afin de définir Zout, il est nécessaire d'obtenir le modèle IBIS ou SPICE du driver de sortie et de le calculer à partir de la courbe VI. La plupart des outils de modélisation SI effectuent ce calcul et affichent l'impédance de sortie. Certains feront même le calcul et recommanderont une valeur de résistance sérielle.

C'est là qu'il peut être particulièrement utile de disposer d'une bibliothèque de composants actualisée et facilement accessible, avec un accès aux informations sur les fournisseurs et des modèles de pièces faciles à mettre à jour. Heureusement, en tant que membre d'Altium Designer, vous avez accès à un large éventail de bibliothèques de composants et à la mise à jour en temps réel des informations sur les fournisseurs, facilement accessibles depuis n'importe quel point de votre équipe de production.

Emplacement des terminaisons des PCB

La question se pose souvent de savoir à quelle distance de l'extrémité d'une ligne de transmission une terminaison doit être placée pour qu'elle puisse travailler correctement. Il serait bon de placer ces résistances sur la surface du circuit imprimé de telle sorte qu'elles ne rendent pas l’agencement ou l'assemblage inutilement difficile.

Le positionnement des résistances parallèles est relativement facile. N'importe quelle position sera parfaite, après l’arrivée du signal à l'entrée de l'appareil, car la forme d'onde de la tension a été délivrée et l'énergie doit seulement être retirée. Sachant cela, placez les terminaisons parallèles après la dernière charge sur la ligne de transmission à l'écart. Il n'est pas nécessaire de les bourrer sous le champ des broches BGA, ce qui facilite le routage du PCB et l'assemblage.

Le positionnement des terminaisons sérielles nécessite un peu plus d'analyse. Comme la résistance de terminaison sérielle ou le circuit de terminaison est destiné à s’additionner à l'impédance caractéristique de sortie du driver, elle donc doit être suffisamment proche. C'est-à-dire que la piste reliant les deux est suffisamment courte pour ne pas fonctionner comme une ligne de transmission isolant une résistance de l'autre. La seule façon d'arriver à une longueur de connexion acceptable est d'utiliser un simulateur pour mesurer la durée de la connexion, en conservant une forme d'onde acceptable au niveau du récepteur. Il s'avérera que la longueur autorisée est une fonction directe du temps de montée du driver. Plus le temps de montée est court, plus la connexion autorisée est courte.

Tronçons et vias

Un tronçon est une branche de la ligne de transmission principale. Dans certaines conditions, un tronçon peut affecter négativement un signal. Lorsqu'un tronçon est assez long, il peut momentanément court-circuiter le signal. La Figure 20 représente une ligne de transmission d'un quart de longueur d'onde à une fréquence F.

Figure 19. Ligne de transmission avec tronçon

La Figure 20 montre une onde sinusoïdale lancée depuis l'entrée de la ligne de transmission. Un quart de longueur d'onde plus tard, ou 90 degrés plus tard, elle arrive à l'extrémité ouverte de la ligne de transmission qui est un circuit ouvert. Comme l’extrémité est ouverte, toute l'énergie est réfléchie sans être inversée. Un quart de longueur d'onde plus tard, elle revient à l'entrée, déphasée de 180 degrés exactement par rapport au signal d'entrée, et l'annule. Ce qui provoque un court-circuit sur la fréquence F.

Les ingénieurs RF utilisent des quarts d'onde comme filtres d'arrêt de bande dans certaines parties des radios, lorsqu’une seule fréquence cause des interférences. Malheureusement, il est rare de trouver dans la logique des points où l'élimination d'une seule fréquence est nécessaire. Au lieu de cela, les tronçons provoquent des inversions de forme d'onde telles que la forme d'onde bleue illustrée dans la Figure 21. Cette inversion de la forme d'onde est gérée par une horloge, ce qui entraîne un double pointage.

Figure 20. Forme d'onde sur ligne de transmission en quart d'onde

Figure 21. Formes d'onde sur une ligne d'horloge montrant les résultats d'un tronçon

La seule méthode fiable pour décider si un tronçon est suffisamment court pour éviter le problème illustré à la Figure 21 est de simuler la topologie proposée dans un outil tel que Hyperlynx et de vérifier si la dégradation de la forme d'onde est acceptable. Comme dans de nombreux circuits actuels, le temps de montée est maintenant très rapide (souvent moins de 100 pSec), la longueur de la piste entre la bille d’une matrice BGA jusqu’au contact réel sur le die lui-même peut être suffisamment longue pour causer un problème. La longueur doit être incluse dans la simulation.

Vias

Le mot Via décrit le trou métallisé utilisé pour connecter la broche de signal d'un circuit intégré à une piste sur une couche interne d'un PCB ou à une piste sur le côté opposé du PCB. Ces vias sont des trous traversants métallisés qui ont à la fois une capacitance et une inductance. L'inductance du via sera d'environ 35 picohenries par mil de longueur (1,4 nanohenries par mm). Le fait que cette inductance pose ou non un problème dépend de la manière dont le via est utilisé.

Si le via sert à connecter un condensateur de dérivation à un plan, ou un fil d'alimentation d'un composant à un plan, cette inductance peut poser un problème avec les signaux ayant un temps de montée très court, ou la dégradation des performances des condensateurs de dérivation.

Gestion de l'empilage des couches et des lignes de transmissions

La plupart des vias sont créés avec des forets de 12 mils (.3 mm) ou moins. Un via créé avec un foret de 12 mm dans un PCB de 100 mils (2,5 mm) d'épaisseur mesurera en moyenne environ 0,3 pF. Un bon simulateur est la meilleure façon de savoir si cette capacitance supplémentaire entraînera ou non un problème d'intégrité du signal. Par expérience, l'auteur a observé que pour des débits de données jusqu'à environ 3 Gb/S, la dégradation d'un via est acceptable.

Une solide gestion de l'empilage des couches intégrée dans votre logiciel de conception de PCB et une transition facile entre la visionneuse des modèles 3D vous aideront à intégrer des vias et à en garder la trace dans vos conceptions. Ne laissez pas la gestion des vias et des microvias créer des risques alors que la ligne d'arrivée est très proche.

Vias dans la visionneuse de modèles 3D d'Altium Designer

Courbes à angle droit

Les effets des courbes à angle droit dans les pistes de signaux est un problème depuis les premiers de la fabrication des PCB. Voici certains des effets mentionnés :

- Les courbes à angle droit provoquent des interférences électromagnétiques.

- Les courbes à angle droit causent des problèmes d'intégrité du signal.

- Les coudes à angle droit provoquent des pièges à acide lors de la fabrication des PCB.

Exemple d'angles sur des pistes après routage.

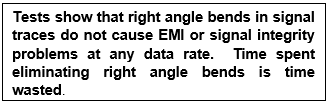

Dans certains cas, beaucoup d'efforts ont été déployés pour s'assurer que les courbes à angle droit soient éliminés. Des systèmes de CAO entiers ont même été mis au rebut parce qu'on ne pouvait pas les empêcher de placer des courbes à angle droit dans les pistes. Une question pertinente serait : Les coudes à angle droit sont-ils un problème avec les circuits logiques ? L’article 1 à la fin de cette section décrit un PCB d'essai construit pour mesurer les effets des courbes à angle droit. Ce PCB a été conçu avec des courbes à angle droit, des courbes à angle aigu et des courbes à angle obtus pour voir à quoi ils ressemblent du point de vue des trois problèmes énumérés ci-dessus. Les tests ont été effectués dans le laboratoire EMI de l'université du Missouri, à Rolla.

Ces tests indiquent qu’aucun des effets des courbes à angle droit ne surviennent en réalité. On peut se demander comment ces idées ont vu le jour. La cause la plus probable est que les ingénieurs RF arrondissent tous les coins. Cela s'explique par le fait que la décharge corona se produit dans les angles aigus à des niveaux de puissance RF élevés.

Ce qui est curieux, c'est que le fait que les courbes à angle droit ne causent pas de problèmes est connu depuis au moins 40 ans, ce qui a été démontré par des tests et des articles publiés. Pourtant, les mythes continuent à se transmettre d'un ingénieur à l'autre.

RÉFÉRENCE POUR LIGNES DE TRANSMISSION ET TERMINAISONS

- « 90 Degree Corners, The Final Turn » Doug Brooks, etal, Printed Circuit Design, janvier 1998.

- SIGNAL INTEGRITY- SIMPLIFIED, Eric Bogatin, Prentice Hall, 2004.

- « Reflections and Crosstalk in Logic Circuit Connections » John A DeFalco, IEEE Spectrum, juillet 1970.

- “Right the First Time, a Practical Handbook on High Speed PCB and System Design, Volumes 1 & 2,” Zasio et Ritchey, Speeding Edge 2003 et 2006.

Garder à l'esprit les principes d'intégrité des signaux ainsi que les lignes de transmission et les principes de terminaison de PCB est un travail en soi. Avec le bon logiciel de conception, une grande partie du travail peut être effectuée pour vous, mais si vous utilisez les bonnes règles de conception et les outils appropriés d'analyse de l'intégrité des signaux, dès le début de la programmation. Assurez-vous que vous utilisez le logiciel de conception qui fera le travail à votre place.

Grâce à des outils de conception avancés, à un environnement unifié et à la vérification intégrée des règles standard de l'industrie, Altium Designer vous permettra de transformer toutes vos idées en réalité. Cliquez sur l'essai gratuit et jugez par vous-même.