Identifying Near-field EMI in a PCB's Power Distribution Network

Any electronic product that is intended for FCC or CE certification needs to pass radiated emissions and EMC testing. If your product doesn’t pass testing, identifying sources of excessive radiated electromagnetic interference (EMI) can be difficult. PCB designers often resort to near-field probe measurements with an oscilloscope to identify offending components or board areas, as well as the frequency content of the radiated EMI. Designers then need to rely on their experience to link radiation at specific frequencies to various EMI sources.

All this takes time, effort, and specialized experience to identify EMI sources and propose solutions. The alternative is to use a field solver to simulate near-field EMI in a PCB directly, as well as evaluate potential solutions to EMI problems. By calculating the electromagnetic field emitted from different regions in a PCB, a field solver can be used to pinpoint an EMI problem to a specific area of the board before a prototyping run. Anytime you can identify and correct an EMI problem before manufacturing, you’ve cut down your development costs and time to market.

With the Ansys SIwave® package, you can access multiple integrated field solvers for signal integrity, power integrity, and EMI analyses. Altium Designer® also provides seamless integration with SIwave through the Ansys EDB Exporter extension, giving designers a simple way to perform these analyses directly from their layout data. To see how this works with an Altium PCB layout, we’ll look at an example Altium Designer project and how excessive near-field EMI can be identified from a series of simulation results.

Near-Field EMI Analysis for a PDN

The Mini PC example project in Altium Designer will be used here for near-field EMI analysis with Ansys SIwave. This particular board contains multiple high-speed interfaces, and any of these could experience power integrity or signal integrity problem. After importing the board geometry and layout into SIwave, a full-wave solution in the frequency domain can be used to identify sources of near-field EMI in the Mini PC board.

The Mini PC contains multiple components and high-speed interfaces that should be investigated for signal integrity and power integrity problems.

- Intel Arria 10 FPGA

- 2 Onboard 8 GB DDR4 DRAM chips running at 1866 MHz

- 2 SODIMM expansion slots for DDR3/4 RAM modules

- USB 3.0, 10/100/1000Base Ethernet, PCIe

Any of these high-speed components and the interconnects between them can act as a source of near-field EMI if not laid out correctly. In order to identify any EMI sources in the board during operation, the EMI Scanner tool in SIwave can be used to automatically check a PCB layout against EMI design rules before running full-wave simulations. This allows problem areas to be identified so that they can be inspected further during a full-wave simulation.

Identifying Problem Areas

The Mini PC layout contains 16 layers with multiple plane-signal-plane layer arrangements for stripline routing. In an initial survey of the Mini PC layout in Altium Designer, we see two stripline DDR4 bus nets (Layer 7) are referenced to the PLL_1V8 power plane (Layer 6, provides 2.5 V to 1.8 V regulation for the FPGA) and to the VDD_DDR power plane without (Layer 8, provides power to the DDR4 modules). Other byte lanes sit on Layer 5, which also use Layers 4 and 6 as their GND reference. As return paths are being established in power planes as displacement currents, there needs to be a low-impedance return path back to the reference potential on the ground plane.

In the Mini PC layout, the only plane in the DDR4 section that doesn’t have a sufficiently low-impedance return path back to ground is Layer 6, specifically the PLL_1V8 net. This low-impedance return path back to the nearest ground planes (Layers 4 and 9) could be provided through decoupling capacitors. One would reasonably expect a near-field EMI problem to arise somewhere in this region as there is low interplane capacitance between PLL_1V8 and the nearest GND nets on Layers 4 and 9.

The PLL_1V8 net in the Mini PC is shown in Figure 1. In this image, we see a region in the PCB layout where discontinuous return paths for the DDR4 nets were identified with the EMI Scanner tool in SIwave. The highlighted region in Figure 1 is the PLL_1V8 net.

Now that EMI Scanner has flagged this net for further inspection, more sophisticated techniques can be used to check whether this EMI design rule violation causes a significant problem in the design. To do this, we can use SIwave to:

- Identify impedance anti-resonances in the PLL_1V8 portion of the power delivery network (PDN) as these could be excited by displacement currents, and

- Simulate near-field radiated EMI before and after the return path problem is fixed.

Let’s look at this in greater depth using the simulation tools in SIwave.

Matching Potential EMI Frequencies to PDN Anti-resonances

The hybrid solver in SIwave can be used to extract broadband Z-parameters for the PLL_1V8 net, which then allows any anti-resonances in the Z-parameter spectrum to be identified. In this case, PDN resonances can be excited if their frequency falls in the bandwidth of the displacement current, which would produce strong ringing on the PDN. This would then radiate a strong electric field in the near-field regime at the PDN anti-resonant frequency.

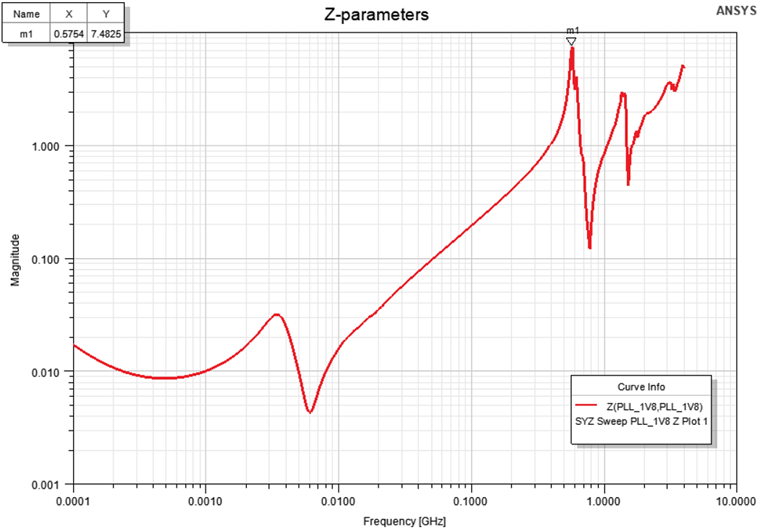

Figure 2 shows the extracted self-impedance for the PLL_1V8 net from 100 kHz to 4 GHz. Note that other Ansys electromagnetic solvers could also be used to extract other Z-parameters for a complex multiple-input multiple-output PDN, such as the transfer impedance between PLL_1V8 and any other power plane.

The PLL_1V8 portion of the PDN has a strong anti-resonance at 580 MHz, so the next logical step is to investigate near-field radiated emission near that frequency. Rather than trying to model discontinuous return paths in the time domain, near-field radiated emissions throughout the PCB can be simulated directly in the frequency domain with the AC Solver option in SIwave.

Near-field EMI Simulation Results

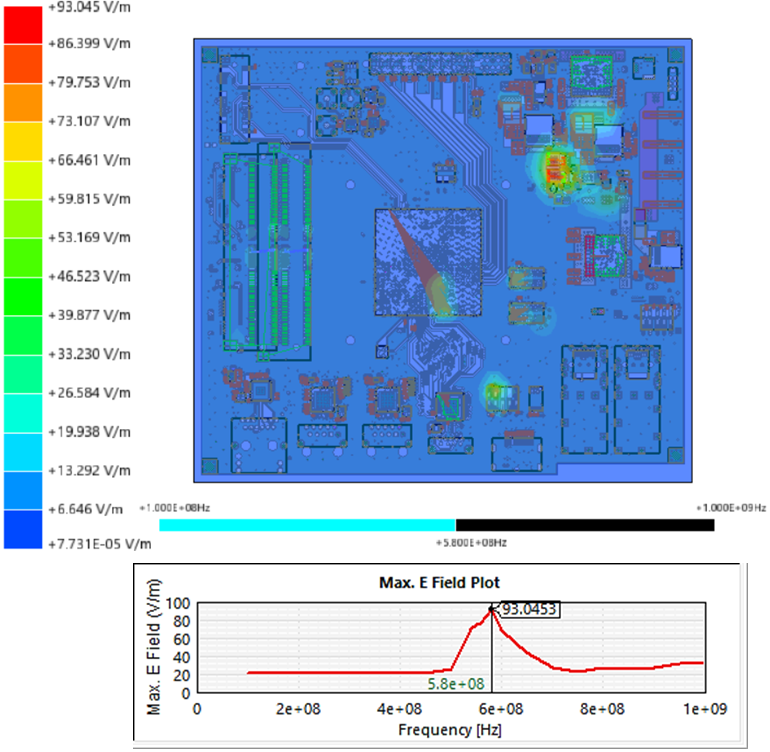

Some initial near-field simulation results due to return currents induced in the PLL_1V8 net are shown in Figure 3. In this figure, we clearly see strong emission near Q4, which supplies power to the PLL_1V8 power plane net (upper-right portion of the region shown in Figure 3). The radiated electric field (magnitude) from this region is orders of magnitude larger than the background electric field in the rest of the board. We also see that this strong EMI is radiated at 580 MHz, corresponding exactly to the PDN anti-resonance.

This motivates two possible solutions to reduce radiated EMI from the PLL_1V8 net:

- Increase the lateral size of the power/ground plane pair to provide higher interplane capacitance.

- Change the layer stackup so that the DDR nets do not reference the power plane.

- Add decoupling capacitors with high self-resonant frequency to the surface layer to damp the anti-resonance in the PDN.

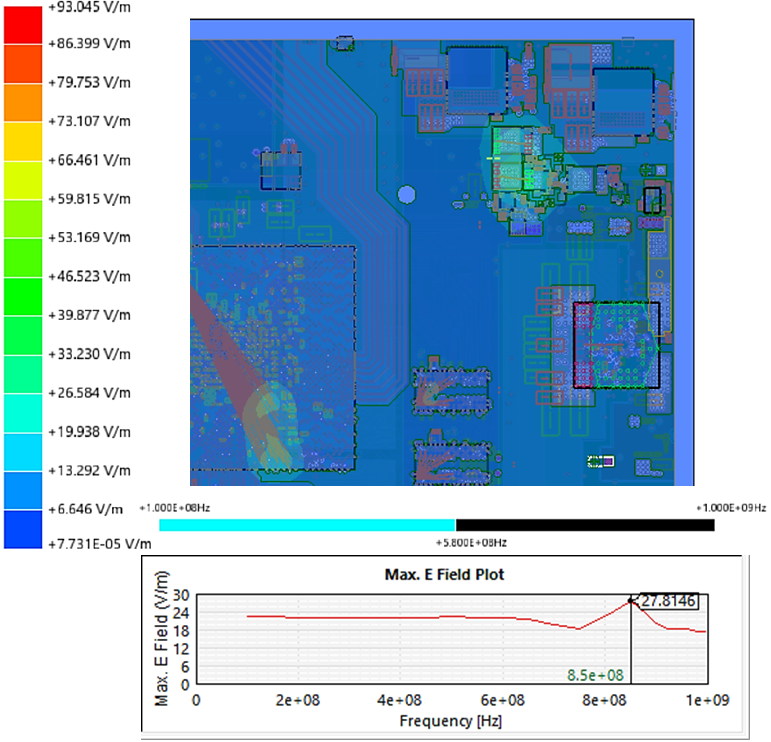

The third route is easiest as pursuing the first two routes in a finished layout could require extensive redesigns. After adding decoupling capacitors, the simulation can be run again and the results can be compared. Figure 4 shows a simulation of the Mini PC board after adding decoupling capacitors on the PLL_IV8 net in Altium Designer.

This result shows that the radiated electric field at 580 MHz in the near-field regime is reduced by ~70% by merely adding decoupling capacitors to the PDN. Solving this PDN problem does more than address a near-field EMI issue; it also reduces phase noise/jitter coupled to other components connected to the PLL_1V8 net.

Summary

The Mini PC example project in Altium Designer was examined in Ansys SIWave to identify potential near-field EMI problems, and a severe problem with near-field radiated emission was located and resolved. By identifying PDN resonances in SIWave and adding some decoupling capacitors to the PDN in Altium Designer, the PDN impedance at the strongest anti-resonant frequency was reduced, thereby reducing the radiated electric field in the near-field regime by ~70%.

The integration provided by Ansys SIwave and Altium Designer makes this type of post-layout simulation workflow quick and easy thanks to Altium Designer’s EDB Exporter extension. PCB designers can use this integration to create advanced PCBs and quickly run post-layout multiphysics simulations for their designs.

Register for the joint Altium and Ansys Webinar to learn more.

3D near-field EMI simulations with real PCBs can be complicated to prepare and implement without the right design and analysis tools. Altium Designer® can interface with Ansys SIwave® using the Ansys EDB Exporter extension, giving you a simple yet powerful way to run power integrity, signal integrity, and EMI analyses in the time domain or frequency domain with a variety of 3D field solvers.