Introducción al diseño de interconexión de alta densidad

Descubra los conceptos básicos de diseño de HDI aquí. Al planificar un diseño HDI, hay una serie de medidas o métricas de rendimiento en relación con el proceso.

Definición de densidad de interconexiones

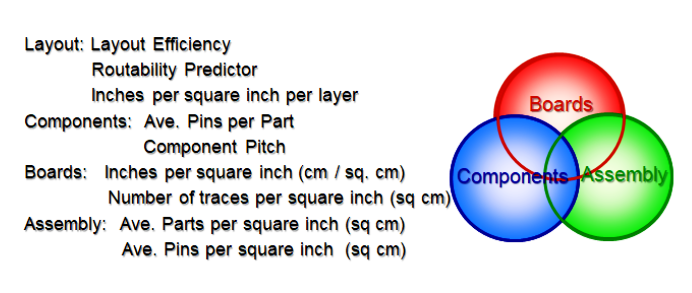

Al planificar un diseño de interconexión de alta densidad (HDI), hay una serie de medidas o métricas de rendimiento en relación con el proceso. Al igual que en el triángulo de la figura 1, estas tres cadenas vitales del proceso HDI son elementos que intervienen en la densidad de las interconexiones.

Métricas en el diseño de interconexión de alta densidad HDI

Complejidad del ensamble

Dos medidas de la dificultad para ensamblar componentes montados en superficie: la densidad de componentes (Cd), medida en piezas por pulgada cuadrada (o por centímetro cuadrado), y la densidad de ensamble (Ad), en patillas por pulgada cuadrada o por centímetro cuadrado.

Encapsulado de componentes

El grado de sofisticación de los componentes: complejidad del componente, (Cc), medida en promedio de patillas (E/S) por pieza. Una segunda métrica es el paso de patilla del componente.

Densidad de placa de cableado impreso

La densidad, o complejidad, de un circuito impreso (Wd), medida en función de la longitud promedio de pistas por pulgada cuadrada de esa placa, incluidas todas las capas de señal. La métrica es pulgadas por pulgada cuadrada, o cm por centímetro cuadrado. Un segundo parámetro es el número de pistas por pulgada lineal o por cm lineal. La densidad de la placa de cableado impreso (PWB) se obtiene asumiendo un promedio de tres nodos eléctricos por red y que el cableado del componente es un nodo de una red. El resultado es una ecuación que indica que la densidad de PWB es 𝝱 multiplicado por la raíz cuadrada de las piezas por pulgada cuadrada multiplicado por el promedio de patillas por pieza. 𝝱 es 2,5 para la región analógica/discreta alta, 3,0 para la región analógica/digital y 3,5 para la región digital/ASIC:

Densidad de PWB (Wd) = 𝝱 √ [Cd] x [Cc]

= 𝝱 √ [piezas por pulg2] x [promedio de patillas por pieza]

Donde: p = número de componentes (piezas)

l = número de patillas de todos los componentes

a = área de la superficie superior de la placa (en pulgadas cuadradas)

Mapa de tecnología de encapsulado

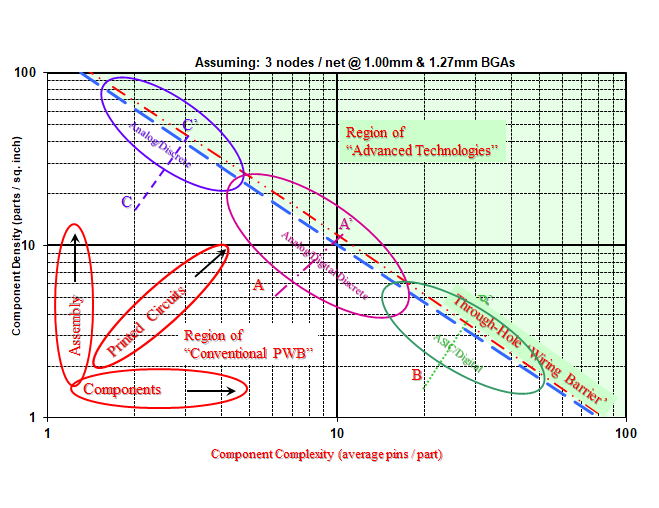

En la figura 2, se muestra a lo que me refiero como mapa de tecnología de encapsulado. El mapa de tecnología de encapsulado lo presentó por primera vez Toshiba en enero de 1991. [1]

Una segunda característica valiosa del mapa es el área de la zona superior derecha. Esta es la «región de interconexiones avanzadas». Aquí es donde es necesario tener una estructura HDI. Las líneas discontinuas indican la barrera o muro de HDI. Al cruzarlas, es donde se vuelve rentable usar HDI. A medida que se avanza, se convierte en una necesidad.

Barrera de cableado de orificio pasante (TH) en función de un ensamble típico

El mapa de encapsulado se crea midiendo el tamaño del ensamble, el número de componentes y las patillas que tienen esos componentes. Los componentes incluyen ambos lados de un ensamble, así como los contactos de borde. Por la simple división de patillas por pieza y piezas por área del ensamble, se conocen los ejes X e Y. El trazado de los componentes por pulgada cuadrada (o componentes por centímetro cuadrado) con relación al promedio de patillas por componente en una representación logarítmica permite calcular la densidad de cableado de PWB en pulgadas por pulgada cuadrada (o en centímetros por centímetro cuadrado) y la complejidad del ensamble (en patillas por pulgada cuadrada o patillas por centímetro cuadrado). La densidad del ensamble es simplemente el eje X multiplicado por el eje Y.

Barrera de cableado de orificio pasante

Cuando se utiliza el gráfico (figura 2) para analizar ensambles de montaje en superficie, aparecen tres zonas principales en el gráfico de encapsulado, y por eso lo llamo mapa. El primer grupo son productos con un alto contenido de dispositivos analógicos y componentes discretos. Ejemplos típicos son las videocámaras, buscapersonas y teléfonos celulares (C-C '). Son los que tienen la mayor complejidad de montaje (hasta 300 a 400 patillas por pulgada cuadrada o 47 patillas por centímetro cuadrado). El segundo grupo son productos con un alto grado de componentes digitales y algunos discretos mixtos. Ordenadores portátiles y de escritorio, instrumentación, equipos médicos y enrutadores de telecomunicaciones son algunos ejemplos (A-A’). El último grupo hace un gran uso de circuitos integrados. PCMCIA, memoria flash, SiP y otros módulos son típicos de este grupo (B-B'). Este grupo tiene la densidad de cableado PWB más alta, con más de 160 pulgadas por pulgada cuadrada (25 centímetros por centímetro cuadrado). En la figura, se muestran vagamente las tres regiones.

Al observar la figura, las líneas de complejidad del ensamble cruzan las líneas de densidad de cableado. En niveles discretos altos, se requiere menos cableado para la densidad de ensamble. En niveles de ASIC altos (y niveles discretos bajos), se requiere mucho más cableado para conectar los componentes. Esto hace que las métricas de ensamble, como patillas por pulgada cuadrada, sean un buen indicador, pero no adecuadas para sustituir la densidad de cableado de PWB.

El proceso general de diseño de PCB

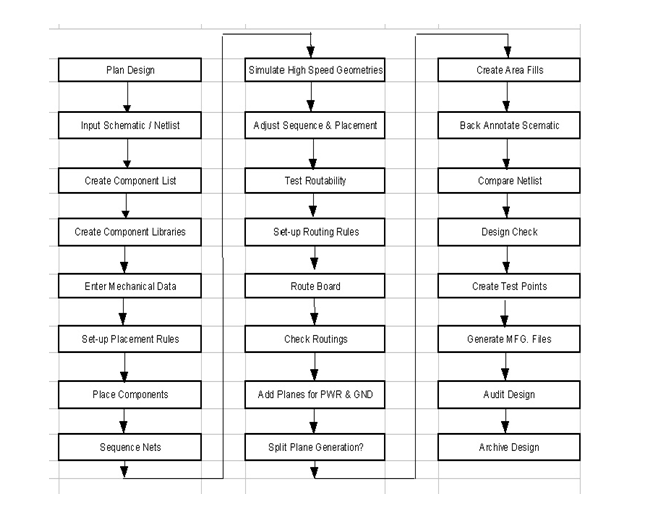

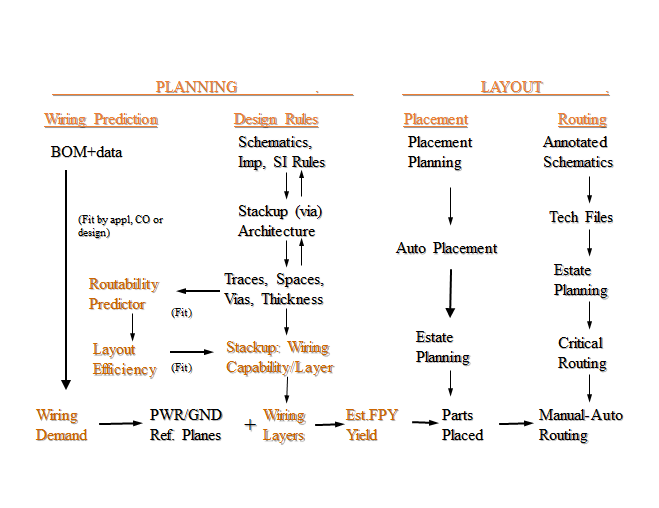

En la figura 3, se muestra el proceso de diseño de PCB utilizando tecnología HDI. Al diseñar con tecnologías HDI, el primer paso, [Diseño del plan], es el más importante. Las eficiencias de enrutamiento en HDI dependen del apilado, la estructura de las vías, la colocación de las piezas, la distribución de BGA y las reglas de diseño, como se muestra en la figura 4. Pero debe tenerse en cuenta toda la cadena de entrega de valor de HDI, incluidos el rendimiento de fabricación, las consideraciones de montaje y las pruebas en circuito. Trabajar con el fabricante y montador de PWB es esencial para el éxito del diseño.

Una descripción general del proceso de diseño y composición de PCB

Directrices, especificaciones, referencias y estándares de HDI

Al abordar el diseño de HDI, un buen punto de partida son las directrices y estándares de IPC. Hay cuatro aplicables específicamente al diseño de HDI, como se muestra en la figura 5.

Proceso de planificación de HDI

- IPC/JPCA-2315: Se trata de una descripción general de HDI y proporciona modelos para estimar la densidad del diseño.

- IPC-2226: Esta especificación instruye a los usuarios en la formación de microvías, selección de densidad de cableado, selección de reglas de diseño, estructuras de interconexión y clasificación de materiales. Tiene como objetivo proporcionar estándares para uso en el diseño de placas de circuito impreso en las que se utilizan tecnologías de microvía. [2]

- IPC-4104: Esta norma identifica los materiales utilizados para las estructuras de interconexión de alta densidad. Las especificaciones de materiales para HDI de IPC-4104 contienen los estándares oficiales que definen muchos de los materiales delgados utilizados en la fabricación de HDI. Estos estándares oficiales se dividen en tres tipos de materiales principales: aislantes dieléctricos (IN), conductores (CD) y conductores y aislantes (CI).

- IPC6016: Este documento cubre el rendimiento y calificación de estructuras de alta densidad.

Directrices y estándares de IPC

Qué cambia en el diseño de HDI

Tres (3) nuevos principios

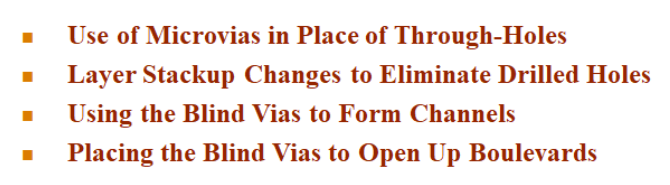

Existen tres (3) principios nuevos para el diseño de HDI con microvías que no existen en el diseño de orificio pasante (TH):

- Las microvías deben reemplazar las vías TH; no solo utilizarse «además de» las vías TH.

- Piense en nuevos apilamientos de capas que permiten la eliminación de las vías TH.

- Las microvías se colocan de tal manera que crean canales y bulevares para mejorar el enrutamiento (consulte la tabla 1).

Sustitución de orificios pasantes (TH) con microvías

La idea principal es que las microvías reemplacen o permitan la eliminación de las vías TH, permitiendo así mejorar la densidad de enrutamiento en las capas internas en 2 o 3 veces. Esto permitirá el uso de menos capas de señal y menos capas de referencia para esas capas de señal.

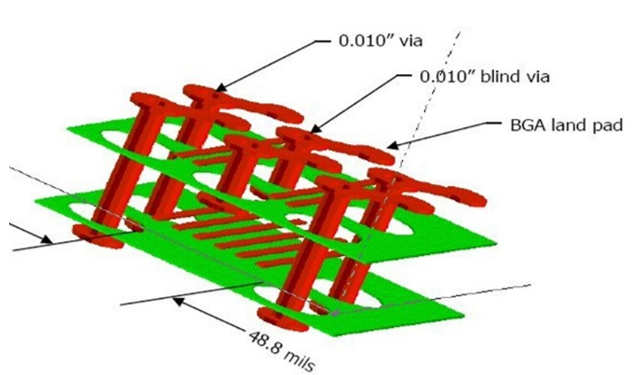

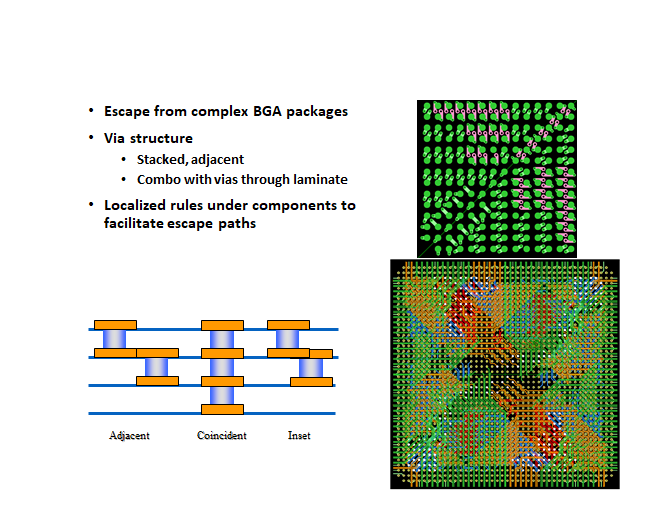

Este principio es más profundo de lo que parece. Esto se debe a que hay tres dimensiones en cuanto se refiere al modo de colocar las microvías (consulte la Figura 6):

Nuevos principios para el diseño de HDI que no se utilizan en multicapa TH

- Las vías ciegas se pueden «desplazar o girar» en el ángulo X-Y o theta para crear más espacio de enrutamiento.

- Las vías ciegas se pueden colocar en la capa interna (3D) para crear aún más espacios de salida.

- La distancia de centro a centro se puede modificar en las capas internas para proporcionar espacio adicional para las pistas.

- Si todo esto sucede en o cerca del lado primario, entonces habrá espacio bajo la BGA en el lado secundario para pistas o, más importante, para componentes discretos, como condensadores de desacople.

Enrutamiento con vías ciegas

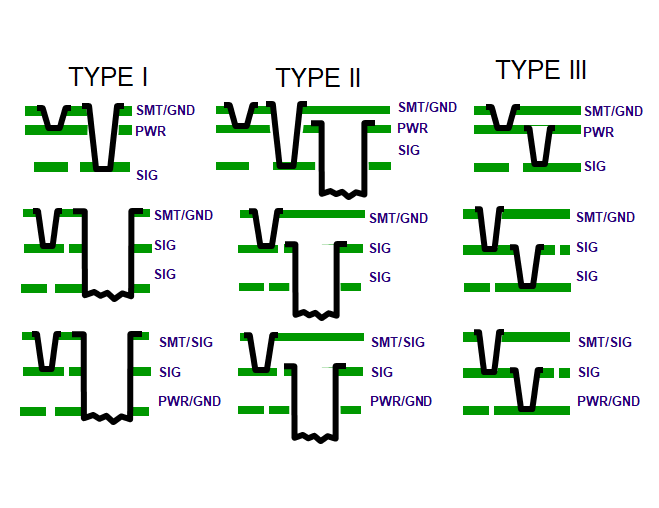

Alternativas del apilado de capas

Si estudia el primer principio y se pregunta: «¿Qué hacen mis vías?» La respuesta es que la vía más común en una PWB son las vías a GND. «¿La segunda vía más común?» La respuesta es obvia, son las vías a PWR. Por lo tanto, mover el plano GND, que generalmente es la capa 2, a la superficie ofrece la posibilidad de eliminar todas esas vías a GND. En la misma línea, mover el plano PWR más usado a la capa 2 permitirá sustituir esos TH por vías ciegas. Esto proporciona cuatro (4) ventajas con respecto al apilado convencional de tipo «microstrip», como se observa en la figura 7:

- No hay líneas finas que metalizar o grabar en la superficie.

- La superficie puede ser un vertido de GND ininterrumpido para reducir las interferencias EMI y RFI (jaula de Faraday).

- Cuanto más próxima esté la capa 2 (PWR) de la capa 1 (GND), más capacitancia planar habrá disponible y menor será la inductancia planar PDN.

- La energía almacenada en la capacitancia planar puede entregarse a componentes con la inductancia en serie más baja disponible, lo que permite la eliminación de la mayoría de los condensadores de desacople.

En la figura 7, se muestran algunos de los apilados de HDI más comunes para reducir el número de vías TH. Se muestran los tres apilados de HDI comunes con las estructuras de tipo IPC (I, II y III).

Los posibles dieléctricos disponibles entre la capa 1 y la capa 2 pueden ser preimpregnados convencionales, preimpregnados perforables por láser, RCC, RCC reforzados o núcleos BC. Estos materiales se describen en el capítulo 2, Materiales de HDI. Si el dieléctrico es delgado, entonces resulta práctico utilizar también una «vía de salto», o «skip», de la capa 1 a la capa 3, ahorrando así el coste de no tener que utilizar una estructura de tipo IPC III. Incluso si no se emplea un dieléctrico delgado, cualquier espesor de dieléctrico inferior a 0,005 pulgadas (

Tres apilados alternativos de capa de superficie comparados con las estructuras IPC de tipo I, II y III

Colocación de vías ciegas para abrir bulevares más grandes

Una técnica útil de diseño de HDI es la de usar vías ciegas para abrir más espacio de enrutamiento en la capa interna. Al utilizar vías ciegas entre las vías pasantes, el espacio de enrutamiento se duplica en las capas internas.

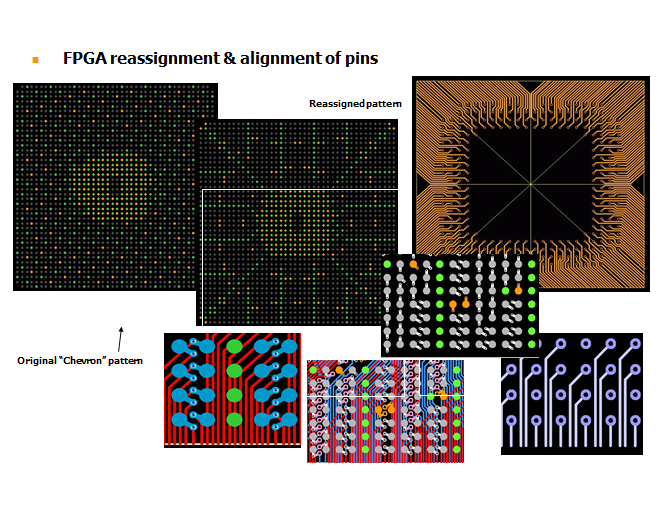

Definición de vía en pad (ViP) parcial y oscilación de ViP para crear canales para enrutamiento

Esto permite utilizar más pistas para conectar pines en las filas internas de una BGA. Como se observa en la figura 6, para esta BGA de 1,0 mm, solo puede haber dos pistas de escape entre las vías de la superficie. Pero bajo las vías ciegas, ahora puede haber seis pistas de escape, lo que aumenta el enrutado en un 30%. Con esta técnica, se requiere un cuarto del número de capas de señal para conectar una BGA compleja de E/S alta. Las vías ciegas están dispuestas para formar bulevares en forma de cruz, en forma de L o en diagonal. El tipo de formación utilizado depende de la asignación de pines de alimentación y tierra. Este es el motivo por el que, para una FPGA, la reprogramación de la colocación de los pines de alimentación y tierra puede ser tan productiva.

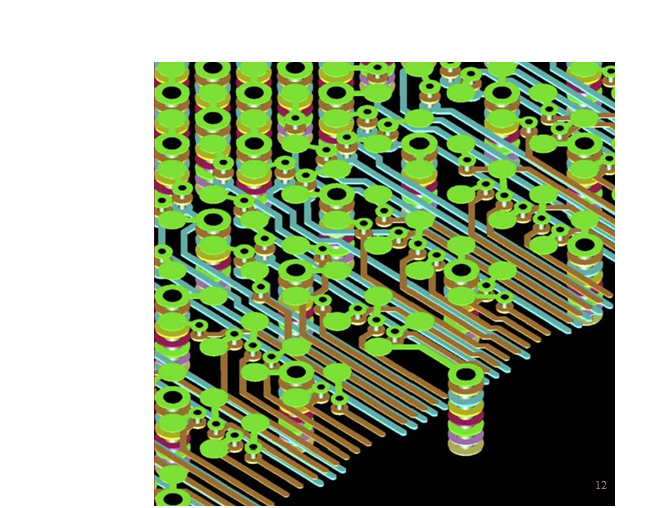

Captura de pantalla de vías ciegas y enrutamiento

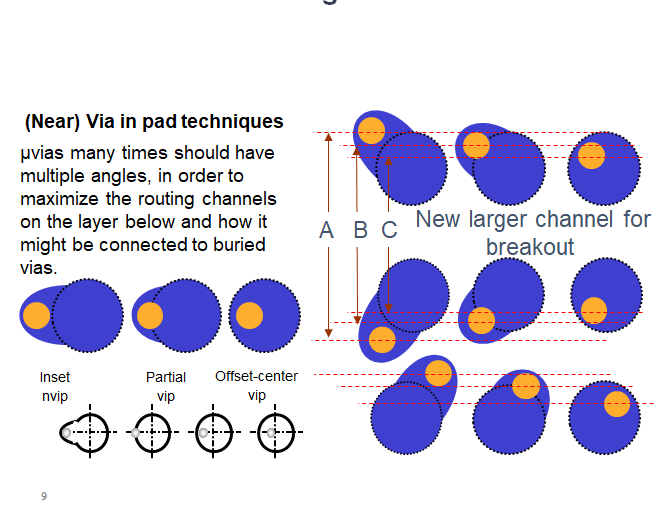

La microvía utilizada para la distribución de BGA se muestra en la figura 9. La microvía se puede colocar fuera del terminal de BGA (encastre), parcialmente dentro/fuera del terminal (ViP parcial) o completamente en "el pad" (ViP); véase la figura 10. Si coloca la vía en el pad, está siempre debe estar «descentrada», y no en el centro del terminal. Esto sirve para minimizar cualquier «vacío» de aire atrapado durante la soldadura. Si la vía se coloca en el centro del terminal de la BGA sin rellenar, al aplicar la pasta de soldadura en el terminal y colocar la BGA en el terminal con pasta, durante el reflujo, a medida que la soldadura se funde, la bola de BGA desciende y atrapa cualquier aire que pueda haber allí, igual que un «corcho en una botella». Al colocar la vía «descentrada», el aire puede escapar a medida que la soldadura se derrite y fluye hacia la microvía.

Alternativas de vías ciegas

Vista en 3D de vías oscilantes

Pruebe estos conceptos básicos de diseño de HDI hoy en Altium Designer. Haga clic en la prueba gratuita.