HDI-BASIS-DESIGN REGELN

Erfahren Sie mehr über die HDI-Design Basis-Regeln. Beim Planen eines HDI-Designs gibt es Leistungsmessungen oder Metriken für den HDI-Vorgang. Vom geschätzten Happy Holden.

Definieren Der Verbindungsdichte

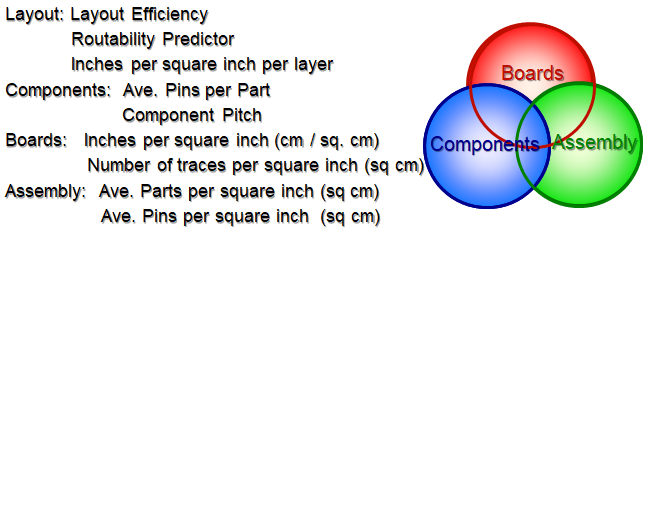

Beim Planen eines HDI-Basis-Designs gibt es Leistungsmessungen oder Metriken für den HDI-Vorgang. Wie das Dreieck in Abbildung 1 sind diese drei wichtigen Ketten des HDI-Prozesses Element der Verbindungsdichte.

HDI-Design Basis-Regeln: ABBILDUNG 1. HDI-Designmetriken

Bestückungskomplexität:

Der Grad der Schwierigkeit beim Zusammenbau der oberflächenmontierten Komponenten kann auf zwei Arten gemessen werden, anhand der Komponentendichte (Cd), gemessen in Bauteilen pro Quadratzoll (oder pro Quadratzentimeter) und die Baugruppendichte (Ad) in Anschlüssen pro Quadratzoll oder Quadratzentimeter.

Komponentenverpackung

Der Grad der Komplexität der Komponenten, Komponetenkomplexität (Cc), gemessen an ihren durchschnittlichen Anschlussflächen (I/Os) pro Bauteil. Eine zweite HDI-Basis-Metrik ist der Abstand der Komponentenanschlussfläche.

Leiterplattendichte:

Die Dichte (oder Komplexität) einer Schaltung, Wd, gemessen anhand der durchschnittlichen Länge der Leiterbahnen pro Quadratzoll der Leiterplatte, einschließlich aller Signallagen. Die Metrik ist Zoll pro Quadratzoll. oder Zentimeter pro Quadratzentimeter. Eine zweite Messung ist die Anzahl der Leiterbahnen pro linearem Zoll oder pro linearem Zentimeter. Für die Ableitung der PWB-Dichte wurde angenommen, dass durchschnittlich drei elektrische Knoten pro Netz bestehen und dass die Komponentenanschlussfläche ein Knoten eines Netzes ist. Das Ergebnis ist eine Gleichung, die besagt, dass die PWB-Dichte multipliziert mit der Quadratwurzel der Bauteile pro Quadratzoll, multipliziert mit den durchschnittlichen Anschlussflächen pro Bauteil 2,5 für den hohen analogen/digitalen Bereich und 3,5 für den digitalen/ASIC-Bereich ist:

PWB-Dichte (Wd) = √ [Cd] x [Cc]

= √ [Teile pro Quadratzoll ] x [ave.leads pro Teil]

Wo:p = Anzahl der Komponenten (Teile)

l = Anzahl der Anschlussflächen für alle Komponenten

a = Bereich der Oberseite der Leiterplatte (Quadratzoll)

Packaging Technology Map für die HDI-Basis

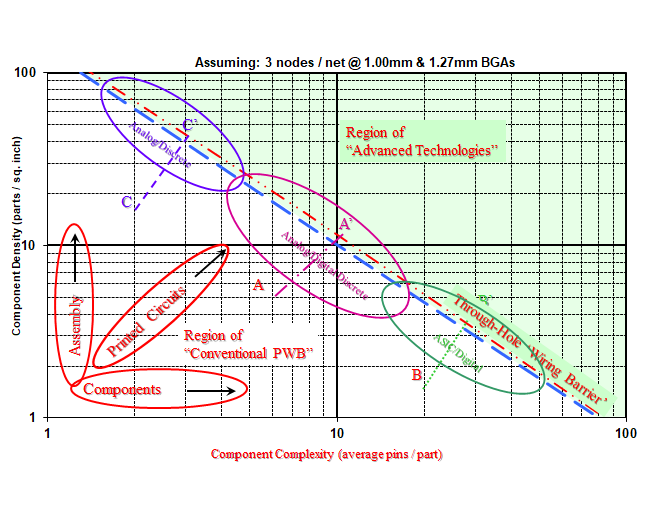

Abbildung 2 zeigt, was ich Packaging Technology Map bezeichne. Die Packaging Technology Map wurde zum ersten Mal im Januar 1991 von Toshiba angezeigt. [1].

Ein zweites wertvolles Merkmal der Map ist der Bereich oben rechts. Dies ist die „Region der erweiterten Verbindungen“. Hier ist eine HDI-Struktur erforderlich. Die gestrichelten Linien zeigen die Barriere oder die Wand des HDI! Wenn Sie diese überschreiten, wird die Verwendung von HDI kostengünstig. Gehen Sie zu weit, wird sie eine Notwendigkeit.

HDI-Basis-Wissen: ABBILDUNG 2 – Die Durchkontaktierung (TH)-Verdrahtungsbarriere als eine Funktion einer typischen Baugruppe.

Für das Erstellen der Packaging Map werden die Baugruppengröße, die Anzahl der Komponenten und die Anschlussflächen jener Komponenten gemessen. Die Komponenten umfassen beide Seiten einer Baugruppe sowie Kantenfinger oder Kontakte. Durch die einfache Aufteilung der Anschlussflächen nach Bauteilen und Bauteile nach Bereich der Baugruppe, sind die X- und Y-Achsen bekannt. Mithilfe der grafischen Darstellung der Komponenten pro Quadratzoll (oder Komponenten pro Quadratzentimeter) gegen die durchschnittlichen Anschlussflächen pro Komponente auf einen Log-Log-Diagramm können die PWB-Drahtdichte in Zoll pro Quadratzoll (oder Zentimeter pro Quadratzentimeter) und die Baugruppenkomplexität (in Anschlussflächen pro Quadratzoll oder pro Quadratzentimeter) berechnet werden. Die Baugruppendichte ist die X-Achse multipliziert mit der Y-Achse.

Durchkontaktierte Verdrahtungsbarriere für das HDI-Basis-Design

Wenn das Diagramm (Abbildung 2) für die Analyse der Oberflächenmontagebaugruppen verwendet wird, erscheinen drei Hauptzonen auf dem Packaging-Diagramm – deshalb nenne ich dies eine Map. Die erste Zone enthält Produkte mit einem hohen Anteil an analogen Geräten und diskreten Komponenten. Typische Produkte sind Camcorders, Pagers und Mobiltelefone ( C-C’). Sie haben den höchsten Montageaufwand. Bis zu 300 bis 400 Anschlussflächen pro Quadratzoll (47 Anschlussflächen pro Quadratzentimeter). Die zweite Gruppe umfasst Produkte mit einem hohen Anteil an digitalen Komponenten und einige gemischte diskrete Komponenten. Beispiele dafür sind Notebooks, Desktop-Computer, Instrumente, medizinische Geräte und Telekommunikationsrouter (A-A’). Die letzte Gruppe verwendet hochintegrierte ICs. PCMCIA, Flash-Speicher, SiPs und andere Module sind typisch für diese Gruppe (B-B’). Diese Gruppe hat die höchste PWB-Verdrahtungsdichte von mehr als 160 Zoll pro Quadratzoll (25 Zentimeter pro Quadratzentimeter). Die Abbildung ist eine ungefähre Darstellung der drei Regionen.

In der Abbildung sehen Sie, dass die Linien der Baugruppenkomplexität die Verdrahtungsdichtelinien kreuzen. Auf hohen diskreten Ebenen ist weniger Verdrahtung für die Baugruppendichte erforderlich. Bei hohen ASIC (und niedrigen diskreten) Ebenen ist viel mehr Verdrahtung für die Verbindung der Komponenten erforderlich. Aus diesem Grund sind die Baugruppenmetriken wie Anschlussflächen pro Quadratzoll ein guter Indikator aber nicht ausreichend, um die PWB-Verdrahtungsdichte zu ersetzen.

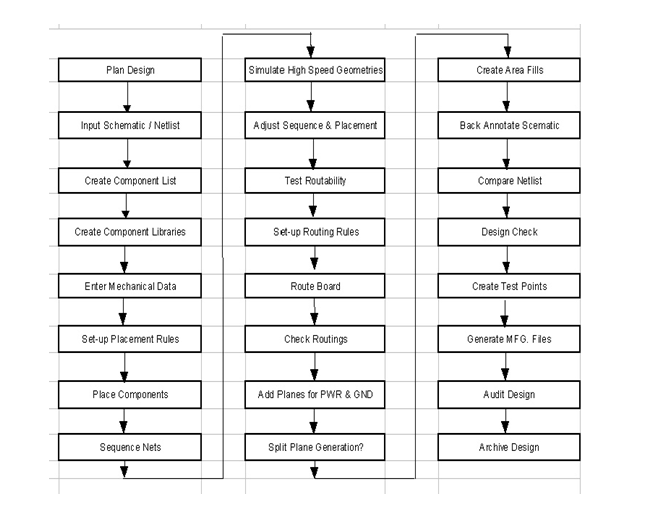

Der Allgemeine Prozess des PCB-HDI-Basis-Designs

Der Prozess des PCB-Designs mithilfe der HDI-Technologie ist in Abbildung 3 dargestellt. Beim Basis-Design mit HDI-Technologien ist der erste Schritt – [Planung des Designs] der wichtigste. Die Effizienz des Routings für HDI hängt von dem Lagenaufbau, der Via-Architektur, der Platzierung der Bauteile, des BGA-Fanouts und der Design-Regeln ab (siehe Abbildung 4). Es muss jedoch die ganze HDI-Wertschöpfungskette berücksichtigt werden, einschließlich Fertigungsausbeute, Aspekte der Baugruppe und In-Circuit-Tests. Die Zusammenarbeit mit Ihrem Leiterplattenhersteller und -monteur ist für ein erfolgreiches Design von entscheidender Bedeutung.

HDI-Basis-Regeln: ABBILDUNG 3 – Ein allgemeiner Überblick des PCB-Designs und Layout-Vorgangs.

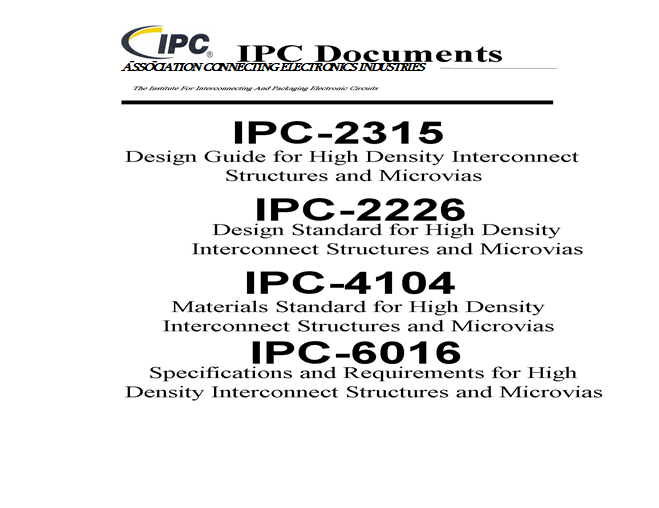

HDI-Design Basis-Standards, Richtlinien, Spezifikationen und Referenzen

Beginnen Sie beim HDI-Basis-Design mit den IPC-Richtlinien und -Standards. Vier beziehen sich speziell auf das HDI-Design (siehe Abbildung 5).

ABBILDUNG 4 – Ein empfohlener HDI-Basis-Planungsprozess für den allgemeinen PCB-Designvorgang

- IPC/JPCA-2315: Dies ist ein Überblick über die HDI und bietet Modelle für die Schätzung der Designdichte.

- IPC-2226: Diese Spezifikation unterrichtet Benutzer in Bezug auf die Bildung der Microvias, der Auswahl der Verdrahtungsdichte, der Auswahl der Design-Regeln, Verbindungsstrukturen und der Materialmerkmale. Sie bietet Standards für das Design von Leiterplatten mithilfe von Microvia-Technologien. [2]

- IPC-4104: Dieser Standard identifiziert die Materialien, die für hochdichte Verbindungsstrukturen verwendet werden. Die IPC-4104 Materialspezifikationen für HDI enthalten Slash-Sheets, die viele der dünnen Materialien, die für HDI verwendet werden, definieren. Die Slash-Sheets der Materialeigenschaften sind in drei Hauptmaterialtypen unterteilt: Die elektrische Isolatoren (IN); Leiter (CD) und Leiter und Isolatoren (CI).

- IPC-6016: Dieses Dokument behandelt die Leistung und Qualifikation für Strukturen mit hoher Dichte.

ABBILDUNG 5 – IPC-Standards und Richtlinien für das HDI-Basis-Design

Was Ist Anders Im HDI-Basis-Design?

DREI (3) NEUE PRINZIPIEN

Drei (3) neue Prinzipien für das HDI-Microvia-Design, die im TH-Design nicht vorkommen.

- Microvias müssen TH-Vias ersetzen und nicht nur „zusätzlich“ zu den TH-Vias verwendet werden.

- Erwägen Sie neue Lagenaufbauten, die die Eliminierung der TH-Vias ermöglichen.

- Platzieren Sie Microvias so, dass sie Kanäle und Boulevards für ein besseres Routing bilden. (Siehe Tabelle 1)

MICROVIAS ERSETZEN DURCHKONTAKTIERUNGEN (TH)

Die Hauptidee ist, dass Microvias TH-Vias ersetzen oder ihre Entfernung ermöglichen, wodurch der Raum, den die TH-Vias belegten, frei wird und sich die Routing-Dichte auf den inneren Lagen um das Zwei- oder Dreifache verbessert. Dies ermöglicht weniger Signallagen und weniger Referenzlagen für diese Signallagen.

Dieser Grundsatz ist bedeutender als es zuerst aussieht. Das liegt daran, dass die Platzierung der Microvias in drei Dimensionen erfolgt (siehe Abbildung 6):

TABELLE 1 – Neue Prinzipien für das HDI-Design, die für Mehrlagen-THs nicht verwendet werden.

- Die Blind-Vias können im X-Y- oder Theta ()-Winkel „verschoben oder geschwenkt“ werden, um zusätzlichen Platz für das Routing zu schaffen.

- Die Blind-Vias können auf inneren Lagen (3D) platziert werden, um zusätzlichen Breakout-Platz zu schaffen.

- Der Abstand von Mitte zu Mitte kann auf den inneren Lagen geändert werden, um zusätzlichen Platz für Leiterbahnen zu schaffen.

- Wenn dies alles auf oder in der Nähe der Primärseite geschieht, dann wird unter dem BGA auf der Sekundärseite Platz für Leiterbahnen oder, noch wichtiger, für diskrete Komponenten wie Glättungskondensatoren geschaffen.