Worum geht es beim PCIe 5.0-Layout und -Routing?

PCI-SIG hat hart daran gearbeitet, die Grenzen der standardisierten Datenraten zwischen Prozessoren und Computerperipheriegeräten zu verschieben. Obwohl der Normenkonzern nicht direkt an der Komponentenentwicklung beteiligt ist, bezeugen die Veröffentlichung der PCIe 5.0-Spezifikation im Jahr 2019 und die bevorstehende Veröffentlichung der PCIe 6.0-Spezifikation im Jahr 2021 die klare Absicht des Konzerns, Peripheriegeräte für datenhungrige Anwendungen zu standardisieren. Einige Anwendungen werden zwangsläufig KI im Rechenzentrum, 5G und ultraschnelle NICs beinhalten.

Eine Verdoppelung der Datenrate von PCIe 4.0 auf 5.0 macht schon jetzt IC- und Packaging-Designern das Leben schwer, aber sie schafft auch Probleme auf Ebene der Leiterplatte und bei den Steckverbindern. Die Ursache für all diese Komplikationen ist die Signalbandbreite, die mit jeder neuen PCIe-Generation auf höhere Frequenzen gehoben wird. Hier erfahren Sie mehr darüber, wie PCB-Designer beim Designen von PCIe-Geräten diese Bandbreitenproblemen bewältigen können.

Verluste in einer PCIe 5.0-Lane

Wie jede Hochgeschwindigkeitsschnittstelle bringt auch PCIe eine Reihe von besonderen Herausforderungen für Layout und Routing mit sich. Die Leiterbahnen, I/Os auf einem IC, Steckverbinder und sogar das Substratmaterial schränken die Bandbreite ein, mit der ein Board unter Beibehaltung spezifikationskonformer Verluste arbeiten kann. Wir haben in diesem Blog eine Vielzahl von Verlustmechanismen diskutiert, daher fasse ich an dieser Stelle kurz die wichtigen Verlustquellen in Hochgeschwindigkeitskanälen (einschließlich PCIe-Lanes) zusammen:

- Leiterverluste: Dies schließt den durch den Leiterquerschnitt bedingten inhärenten Gleichstromwiderstand ein.

- Dielektrische Verluste: Anregung und Relaxation im PCB-Substrat dämpfen das elektrische Feld, während es sich durch einen Hochgeschwindigkeitskanal ausbreitet.

- Verluste aufgrund Kupferrauheit: Alles geätzte Kupfer auf PCB-Laminaten ist rau (sowohl galvanisiert als auch gewalzt), und die Kupferrauheit muss bei der Durchführung von Impedanzberechnungen korrekt modelliert werden.

- Resonanzleistungsverlust: Dieser Glasfasergewebeeffekt resultiert aus der periodischen Belastung in losen Glasfasergeweben, was bei bestimmten Frequenzen zu Leistungsverlusten führt, wenn Hohlräume im Substrat angeregt werden.

Es ist zu beachten, dass Strahlungsverluste auch bei Mikrostreifen zu berücksichtigen sind, wenn die Substratdicke ziemlich groß ist (z. B. 30 mils in diesem technischen Artikel von John Coonrod), aber diese Verluste können bei geschlossenen Wellenleitern oder beim Streifenleitungsrouting ignoriert werden. Diese Verluste können auch bei Leiterplatten mit höherer Lagenzahl oder bei Mikrostreifen auf sehr dünnen Laminaten vernachlässigt werden. Angesichts der Datenübertragungsraten von 32 Gbps gemäß PCIe 5.0 ist FR4 keine realisierbare Option mehr und es muss ein verlustarmes Laminat verwendet werden.

Bei PCIe 5.0-Kanälen können dielektrische und Rauheitsverluste auf Ebene des Leiterplattensubstrats ausgeglichen werden, indem man geeignete verlustarme Laminate auswählt. Gegensteckverbinder und Vias fügen ihre eigenen Verluste hinzu, normalerweise in Form einer durch Impedanzfehlanpassungen bedingten Reflexion innerhalb der Signalbandbreite. Die Verluste sind bei der PCIe 5.0-Spezifikation begrenzt und auf -37 dB gemäß der Nyquist-Frequenz einer Lane (16 GHz bei einer Bitrate von 32 Gbps) reduziert. Die Weise, wie Sie Ihre Komponenten auf einem Board oder auf mehreren Boards anordnen, bestimmt die Anzahl der Vias, Steckverbinder und die maximale Verbindungslänge, die Sie beim PCIe 5.0-Layout und -Routing verwenden können.

Layout- und Routing-Optionen

Topologie und Steckverbinder

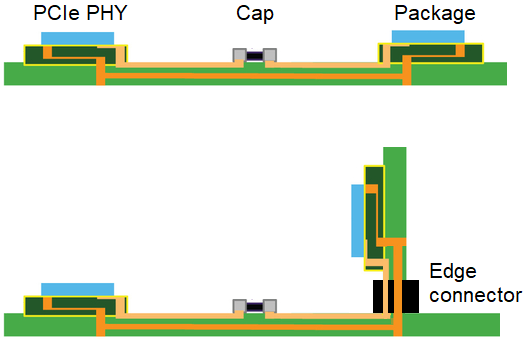

Sobald Sie sich für ein PCB-Substratmaterial entschieden und Leiterbahnen mit ausreichend niedrigen Verlusten entworfen haben, können Sie mit dem Routing und Layout für PCIe-Geräte fortfahren. PCIe-Geräte, Daughterboards und Host-Prozessoren werden in einer Punkt-zu-Punkt-Topologie angeordnet. PCIe-PHY-Module, -Geräte und -Prozessoren können auf demselben Board oder über einen Steckverbinder getrennt auf verschiedenen Boards (orthogonal, Rand oder mezzanin) platziert werden.

AC-Koppelkondensatoren

Ein wichtiger Punkt beim Routing von PCIe-Links ist die Platzierung eines AC-Koppelkondensators. Wenn Sie noch nie mit PCIe gearbeitet haben, ist dies einer der Punkte, die auf einem Datenblatt leicht übersehen werden. Verschiedene IC-Hersteller werden unterschiedliche Werte für AC-Koppelkondensatoren für ihre Produkte empfehlen (z. B. für FPGA von Xilinx werden 100 nF empfohlen). Wie bei jedem anderen Koppelkondensator besteht der Zweck darin, den DC-Offset entlang der beiden Enden des Links zu entfernen, aber dabei gleichzeitig die Ausbreitung von Datenimpulsen zwischen den Komponenten zu ermöglichen.

Impedanz von Leiterbahnen und Steckverbindern

Beim Routing in PCIe-Lanes sollten die Best Practices für differenzielle Signale befolgt werden (85 Ohm differenzielle Impedanz mit Längenanpassung über eine Diff-Paar-Netzklasse und ordnungsgemäße Abstände). Es ist zu beachten, dass es bei PCIe-konformen Steckverbindern, die zwischen langen Leiterbahnabschnitten platziert werden, häufig zu großen Impedanzabweichungen (bis zu 15 Ohm) kommt. Wichtiger ist, wie sich diese Fehlanpassung auf die S-Parameter (insbesondere die Rückflussdämpfung) auswirkt. Diese Auswirkung muss anhand von Tests ermittelt werden, um zu prüfen, ob ein Steckverbinder, ein Lagenübergang oder ein allgemeiner Routing-Stil akzeptabel ist.

Fertigstellung und Prüfung

Wenn es an der Zeit ist, einen Prototyp oder einen Testcoupon zu testen, kann gemäß PCIe 5.0-Spezifikation ein differenzieller Breakout-Kanal von einem Prüfling zu einer Testvorrichtung geroutet werden. Um den Verlust in Ihrem PCIe-Kanal zu bewerten, platzieren Sie einen identischem Breakout-Kanal auf dem Board und verwenden Sie diesen, um die S-Parameter für den Kanal zu "de-embedden". Hierdurch können Sie feststellen, ob die Kanäle den PCIe 5.0-Spezifikationen entsprechen und ob weitere Designänderungen erforderlich sind.

Während wir darauf warten, dass mehr PCIe 5.0-kompatible Geräte auf den Markt kommen, kann es nicht schaden, schon einmal damit anzufangen, nach diesen Spezifikationen zu designen. Intels PCIe 5.0/DDR5-kompatible Sapphire Rapids-CPUs werden 2021 verfügbar sein, und AMD wird 2022 mit Konkurrenzprodukten nachziehen. Glücklicherweise sind die PCIe 5.0-Spezifikationen elektrisch rückwärtskompatibel mit früheren PCIe-Generationen. Und wahrscheinlich wird es danach nicht mehr lange dauern, bis wir über PCIe 6.0 sprechen.

Wenn Sie bereit sind, mit dem Design eines PCIe 5.0-Layouts zu beginnen und Signale auf Ihrem Board zu routen, benötigen Sie die Hochgeschwindigkeits-Designtools von Altium Designer®. Damit verfügen Sie über die Tools, die Sie benötigen, um Hochgeschwindigkeitsboards für jede Anwendung zu routen und sie für die Massenfertigung vorzubereiten. Und sofern Sie mit anderen Mitgliedern Ihres Design-Teams kollaborieren, können Sie Revisionen über die Altium 365®-Plattform freigeben und verfolgen - eine elegante Lösung, mit der die Designer von zu Hause aus arbeiten und eine noch nie dagewesene Effizienz erreichen können.

Wir haben nur ganz oberflächlich behandelt, was mit Altium Designer auf Altium 365 möglich ist. Wenn Sie mehr erfahren möchten, können Sie die Produktseite besuchen, wo Sie Zugang zu detaillierterem Beschreibungen der Funktionen und On-Demand-Webinaren haben.