In cosa consiste il layout e il routing PCIe 5.0?

PCI-SIG si sta impegnando per oltrepassare i limiti delle velocità di trasmissione dati standardizzate tra processori e periferiche dei computer. Anche se il gruppo di standard non ha un ruolo diretto nello sviluppo dei componenti, il rilascio della specifica PCIe 5.0 nel 2019, oltre all'imminente rilascio della specifica PCIe 6.0 nel 2021, mostrano un chiaro intento di standardizzare le periferiche per tutte quelle applicazioni che richiedono un gran numero di dati. Alcune applicazioni includeranno inevitabilmente l'Intelligenza Artificiale nel centro dati, il 5G e Controller ad Interfaccia di Rete (NIC) ultra-veloci.

Un raddoppio della velocità di trasmissione dati, da PCIe 4.0 a 5.0, complica di fatto il lavoro dei progettisti di circuiti integrati e imballaggi, oltre a creare problemi relativi ai PCB e ai connettori di accoppiamento. Tutto deriva dalla larghezza di banda del segnale, che raggiunge frequenze sempre più alte a seguito di una nuova generazione di PCIe. Ecco come i progettisti PCB dovranno far fronte a queste difficoltà relative alla larghezza di banda durante la progettazione di dispositivi PCIe.

Perdite in una pista PCIe 5.0

Come qualsiasi interfaccia ad alta velocità, lo standard PCIe presenta una particolare serie di sfide per il layout e il routing. Le tracce, gli Input/Output su un circuito integrato, i connettori e persino il materiale del substrato, fissano dei limiti sulla larghezza di banda che una scheda può ospitare, mantenendo le perdite all'interno delle specifiche. In questo blog abbiamo discusso una varietà di meccanismi di perdita, quindi riassumerò brevemente le più importanti fonti di perdita nei canali ad alta velocità (comprese le piste PCIe) qui di seguito:

- Perdite del conduttore: Include la resistenza tipica in corrente continua dovuta alla sezione trasversale del conduttore.

- Perdite dielettriche: Le stimolazioni e le distensioni nel substrato PCB attenuano il campo elettrico mentre si propaga attraverso un canale ad alta velocità.

- Perdite di rugosità del rame: Tutto il rame inciso sui laminati PCB è ruvido (sia elettrodepositato che laminato) e la rugosità del rame deve essere modellata correttamente durante l'esecuzione dei calcoli d'impedenza.

- Perdita di risonanza elettrica: Questo effetto di trama della fibra risulta dal carico periodico in trame di fibre sciolte, con conseguente perdita di alimentazione a particolari frequenze, poiché gli alloggiamenti nel substrato sono stimolati.

Notare che le perdite d'irradiazione dovrebbero essere considerate anche nelle microstrip quando lo spessore del substrato è piuttosto ampio (ad esempio, 0,75 mm in questo articolo tecnico di John Coonrod), anche se queste perdite possono essere ignorate in riferimento a guide d'onda chiuse o nel routing della stripline. Queste perdite possono inoltre essere ignorate in schede con un maggior numero di layer o per microstrip su laminati molto sottili. Nei PCIe 5.0 con velocità di trasmissione dati pari a 32 Gbps, l'utilizzo di un FR4 non è più un'opzione praticabile e deve essere sostituito con un laminato a bassa perdita.

Nei canali PCIe 5.0, le perdite dielettriche e di rugosità possono essere indirizzate a livello del substrato PCB, selezionando gli appropriati laminati a bassa perdita. I connettori di accoppiamento e le vias contribuiranno alle proprie perdite, normalmente attraverso la riflessione dovuta alla mancata corrispondenza d'impedenza all'interno della larghezza di banda del segnale. Le perdite nelle specifiche PCIe 5.0 sono limitate a -37 dB rispetto alla frequenza Nyquist di una pista (16 GHz per un bitrate di 32 Gbps). La modalità di disposizione dei componenti su una scheda, o su più schede, determinerà il numero di vias, di connettori e la lunghezza massima di interconnessione che puoi utilizzare nel layout e nel routing PCIe 5.0.

Opzioni di layout e routing

Topologia e connettori

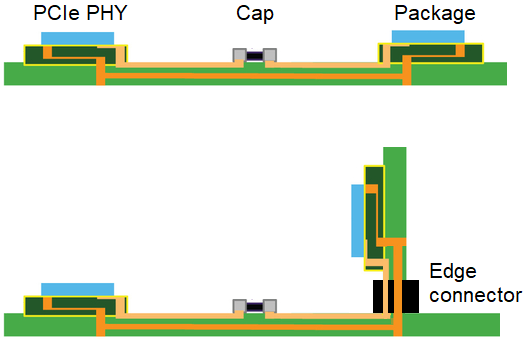

Dopo aver applicato il materiale del substrato PCB e aver progettato le tracce, in modo da avere perdite sufficientemente basse, puoi procedere con il routing e il layout dei dispositivi PCIe. I dispositivi PCIe, le schede figlie e i processori host, sono posizionati mediante una topologia point-to-point. I moduli, i dispositivi e i processori PCIe PHY possono essere posizionati sulla stessa scheda, oppure divisi su schede differenti con un connettore (ortogonale, bordo o mezzanino).

Condensatori di accoppiamento in corrente alternata

Un aspetto importante nel routing dei collegamenti PCIe consiste nell'inserire un condensatore di accoppiamento in corrente alternata. Se non hai mai lavorato con un PCIe, questo è uno di quegli aspetti che potrebbero essere racchiusi in un datasheet. Diversi rivenditori di circuiti integrati consiglieranno diversi parametri riferiti ai condensatori di accoppiamento in corrente alternata per i loro prodotti (ad esempio, i dispositivi logici programmabili Xilinx consigliano 100 nF). Come qualsiasi altro condensatore di accoppiamento, lo scopo è quello di rimuovere l'offset in corrente continua lungo ciascuna estremità del collegamento, consentendo agli impulsi dei dati di propagarsi fra i componenti.

Impedenza di traccia e del connettore

Il routing nelle piste PCIe dovrebbe seguire le migliori pratiche per i segnali differenziali (impedenza differenziale di 85 Ohm con una corrispondenza della lunghezza attraverso una classe di rete della coppia differenziale e una corretta spaziatura). Notare che, per i connettori posizionati fra lunghe sezioni di tracce, è comune osservare ampie deviazioni d'impedenza (fino a 15 Ohm) su connettori compatibili con i PCIe. La cosa più importante è il modo in cui questa mancata corrispondenza influisce sui parametri S (in particolare, l'attenuazione di riflessione), che deve essere determinata dai collaudi per verificare se un connettore, una transizione del layer, oppure un generico stile di routing siano accettabili.

Finitura e collaudo

Al momento di collaudare un prototipo o verificare i collaudi ottenuti, la specifica PCIe 5.0 consente di indirizzare un canale di breakout differenziale da un DUT ad un dispositivo di prova. Per valutare la perdita nel tuo canale PCIe, devi inserire sulla scheda un canale di breakout identico e utilizzarlo per estrarre i parametri S riferiti al canale. In seguito, puoi determinare se i canali soddisfino le specifiche PCIe 5.0 e se ulteriori modifiche di progettazione siano necessarie.

Fino a quando non saranno disponibili sul mercato altri dispositivi compatibili con i PCIe 5.0, progettare secondo queste specifiche può essere una buona soluzione. Le CPU Sapphire Rapids, compatibili con i PCIe 5.0/DDR5 di Intel, saranno disponibili nel 2021 e AMD svilupperà prodotti competitivi nel 2022. Fortunatamente, le specifiche PCIe 5.0 sono elettricamente compatibili con le precedenti generazioni di PCIe. Probabilmente, a breve sentiremo già parlare di PCIe 6.0.

Quando sei pronto per iniziare a progettare un layout PCIe 5.0 e indirizzare i segnali sulla tua scheda, hai bisogno degli strumenti di progettazione ad alta velocità di Altium Designer®. Avrai a disposizione gli strumenti necessari per eseguire il routing delle schede ad alta velocità su qualsiasi applicazione e organizzare il processo di produzione su larga scala. Al momento di dover collaborare con altri membri del tuo gruppo di progettazione, potrai condividere e tenere traccia delle revisioni attraverso la piattaforma Altium 365, consentendo ai progettisti di lavorare da casa e raggiungere livelli di efficienza senza precedenti.

Questo è solo un piccolo esempio di ciò che è possibile realizzare con Altium Designer® tramite Altium 365. Puoi verificare la pagina prodotto per una descrizione più approfondita delle funzionalità, oppure assistere ad uno dei webinar on-demand.