Сквозная (fly-by) топология на платах памяти DDR3 и DDR4

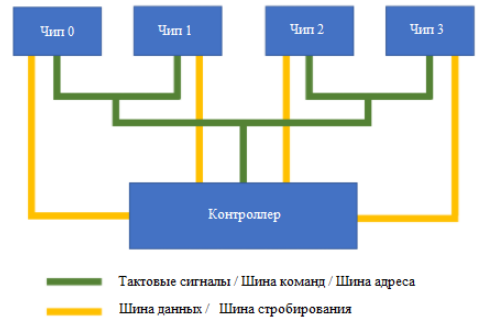

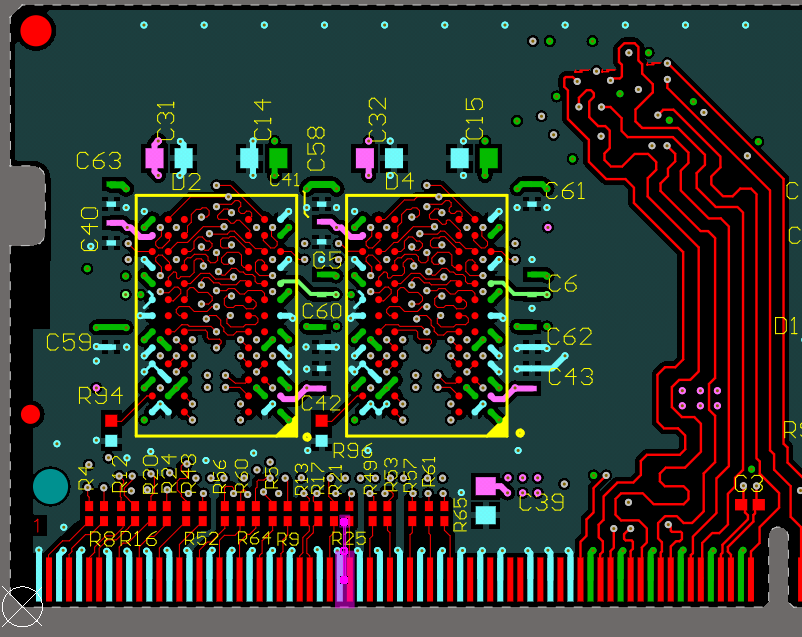

Когда в следующий раз будете проводить апгрейд своего компьютера или ноутбука, взгляните на чипы оперативной памяти (ОЗУ). При необходимости используйте увеличительное стекло. Все проводники, которые вы сможете увидеть на верхнем слое печатной платы, будут лишь началом сложной сети трасс между торцевым разъемом и чипами памяти. На первый взгляд эта топология может выглядеть очень сложной, но если взглянуть на неё “издалека”, то можно заметить, что в ней имеется относительно простой шаблон.

Этот относительно простой шаблон топологии известен под названием “сквозная топология”, или топология Fly-by. Схема разводки при выполнении сквозной топологии является более предпочтительной по сравнению топологией выполненной по принципу двух Т-образных соединений, или Double-T, из-за множества причин связанных с целостностью сигналов. Применение сквозной топологии приводит к уменьшению числа одновременных коммутационных помех и позволяет протоколам DDR справляться с перекосами, которые возникают из-за применения сквозной топологии, за счет поддержки выравнивания уровней записи. Она также хорошо работает с высокочастотными приложениями и сокращает количество и глубину неиспользуемых частей колодцев переходных отверстий, так называемых “стабов” (stubs).

Разводка DDR: по принципу двух Т-образных соединений или с применением сквозной топологии

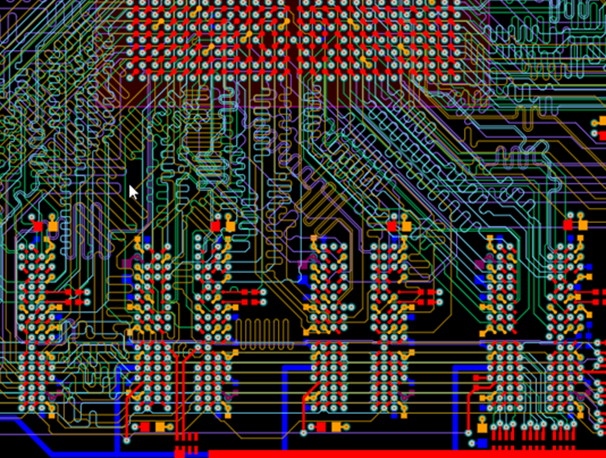

Сквозная топология имеет структуру гирляндного соединения с очень короткими “стабами” или вовсе без них. Благодаря такой структуре сквозная топология имеет меньшее число разветвлений и соединений точка-точка. При разводке DDR3 и DDR4, сквозная топология начинается с контроллера проходит через Чип 0 и далее через все чипы памяти вплоть до Чипа N или до старшего бита данных. Разводка выполняется по порядку номеров байтовых дорожек, байтовые дорожки данных разводятся в одном слое. Разводку можно упростить при необходимости, поменяв местами биты данных внутри байтовых дорожек. Пример сквозной топологии приведен ниже.

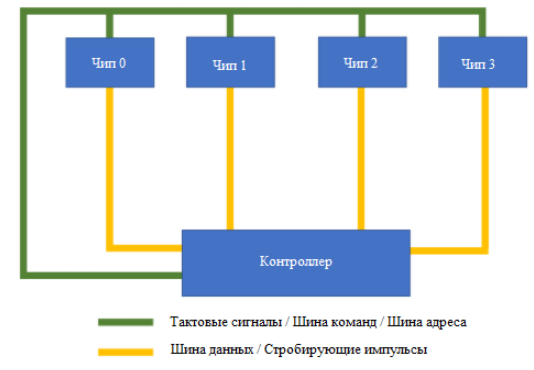

Альтернативным способом разводки DDR плат, является способ по принципу двух Т-образных соединений или топология Double-T. При использовании данной топологии, дифференциальные тактовые цепи, цепи команд и адреса выходят группой из контроллера памяти и образуют Т-образное соединение, которое может поддерживать два чипа. Каждая ветвь может разделяться снова для поддержки ещё двух чипов, таким образом поддерживая до четырех чипов. В общем, 2N чипов может быть соединено по принципу двух Т-образных соединений (N-количество ветвей топологии). Каждая отдельная секция впоследствии присоединяется к отдельному чипу оперативной памяти. Шины данных и стробирования разводятся напрямую от контроллера памяти к каждому чипу оперативной памяти. Это показано на рисунке ниже.

Т-образные топологии были широко распространены при разводке DDR2, но каждое разветвление создает накопленную разницу импедансов даже на частотах DDR2. Таким образом, сквозная топология является более предпочтительной в DDR3 и более поздних поколениях оперативной памяти, так как к каждому устройству подходит отдельная ветвь тактовых, адресных и командных цепей. В частности, для устройств ОЗУ с одним кристаллом предпочтительна сквозная топология, тогда как в устройствах с несколькими кристаллами может использоваться любая топология. Фактически существует некоторая свобода выбора между этими различными топологиями, но DDR3 и DDR4 проще развести используя сквозную топологию, из-за преимуществ в целостности сигналов.

Рекомендации по компоновке и разводке DDR при использовании сквозной топологии

При использовании сквозной топологии есть несколько основных рекомендаций, которых следует придерживаться при разводке проводников, для обеспечения целостности сигналов. Во-первых, это определение необходимого стека слоев печатной платы и выбор ориентации чипов. Если на плате достаточно места, то тактовые проводники, проводники адреса, команд и управления, должны быть расположены в одном слое, но можно сэкономить место, разводя проводники в разных слоях при необходимости. Разводка тактовых проводников, проводников адреса, команд и управления идет от чипа младшего бита данных к чипу самого высокого бита данных. Между микросхемами памяти должно быть расстояние не менее 5 мм (200 мил). Наконец, необходимо установить дифференциальную нагрузку в 100 Ом на последнее устройство SDRAM в цепи.

Когда вы начинаете размещать компоненты, важно выделить место для разветвления проводников, выходящих из-под корпуса элемента (так называемого «фэнаута»), оконечных резисторов и оконечных источников питания. Кроме того, ваша стратегия трассировки не должна допускать прохождения проводников через пустоты переходных отверстий на полигонах. Переходные отверстия должны быть расположены достаточно широко для возможности провести между ними два или более проводников.

Грамотно выполненный фэнаут увеличивает количество каналов трассировки. Обратите внимание, что сквозная топология подразумевает добавление некоторого перекоса между всеми сигнальными линиями. Это снижает уровень коммутационных помех при переключении одной микросхемы. Фактически, соседние микросхемы не будут затронуты, поскольку есть некоторая задержка между переключениями разных микросхем. Помимо целостности сигнала, есть и другие моменты, которые следует учитывать при разводке устройств с DDR3 и DDR4.

Целостность сигнала при использовании сквозной топологии для DDR3 и DDR4

Если вы выполняете разводку дифференциальных пар на внутренних слоях, то их можно считать как полосковые или двойные полосковые линии. Проводники верхнего слоя следует трассировать как микрополосковые линии. Все линии передач нуждаются в контроле импеданса для подавления отражений на всех межсоединениях и на приемнике. Рекомендуется, чтобы одиночные проводники имели импеданс в 50–60 Ом (дифференциальный импеданс 100–120 Ом) для большинства интерфейсов.

Обратите внимание, что спецификация JEDEC для DDR3 определяет два режима работы источника на 34 и 40 Ом для несимметричных входов / выходов. Однако современные устройства используют оконечную нагрузку на кристалле для согласования с соответствующими значениями характеристического импеданса. Обязательно проверьте входной и выходной импедансы ваших компонентов и при необходимости примените согласование.

Один из подходов к достижению большей чувствительности к сигналу и ограничениям, подразумевает объединение байтовых дорожек данных. Это упростит процесс разводки, но будьте внимательны к зазорам между проводниками в линиях, чтобы предотвратить чрезмерные перекрестные помехи внутри линии. Связанные сигналы должны быть тщательно согласованы по длине в соответствии с рекомендациями, указанными в технических характеристиках вашего устройства, хотя будьте осторожны, поскольку они обычно предполагают значение диэлектрической постоянной Dk, равное 4 для материала платы.

Если вы выполняете трассировку на материале печатной платы с другим значением Dk, то вам необходимо согласовать длины проводников, чтобы компенсировать допустимую временную задержку (или фазовую задержку на дифференциальных парах).

Для зазоров между проводниками во многих рекомендациях указываются разные значения, но их легко выяснить исходя из контекста. Будьте осторожны при выборе зазоров между проводниками и дифференциальными парами, если они указаны в примечаниях по применению, поскольку эти значения зачастую предполагают определенный стек слоев.

Следует выдерживать точное расстояние между концами дифференциальных пар, чтобы обеспечить требуемый дифференциальный импеданс. Более широкие проводники могут обеспечить более плотную маршрутизацию, поскольку они будут иметь более низкую индуктивность, которая является основным источником перекрестных помех на реальных частотах DDR. Лучше всего запустить моделирование перекрестных помех, чтобы проверить предельные зазоры между одиночными и дифференциальными проводниками.

Использование Altium Designer® для выполнения сквозной трассировки

Учитывая сложность трассировки и большое количество проводников, вам следует использовать электрическую схему в качестве фундамента вашего проекта. Имея схему под рукой, вы можете найти ключевые компоненты и цепи. С помощью этого метода вы можете использовать перекрестный выбор компонентов схемы и цепей для выделения их на плате (Cross Selection Mode, Cross Probe). Эти функции в сочетании с настройками правил проектирования помогут вам определить дифференциальные пары, которые нуждаются в согласовании длины, помогут поддерживать целевой импеданс и необходимый зазор во время трассировки.

Конструкции высокоскоростных печатных плат сложны и требуют планирования размещения компонентов и контроля импеданса. Altium Designer предоставляет вам полный набор управляемых правилами интерактивных инструментов разводки для реализации топологии Fly-by в проектах с DDR3 и DDR4. В целом, вы должны выполнять трассировку, которая обеспечит прямой путь и правильное соединение всех цепей шины. Функции редактора плат САПР Altium Designer упрощают создание проекта с DDR3 и DDR4 с обеспечением простоты трассировки и целостности сигнала.

Ознакомьтесь со статьями, приведенными ниже, чтобы узнать больше о топологии и трассировке DDR3/DDR4:

- Интерфейсы и топология устройств памяти DDR3 в конструкции платы

- Как трассировать устройства памяти DDR3 и создавать фэнауты ЦПУ

- Виртуальные уроки Altium Academy: Создание трассировки и фэнаутов DDR и BGA

Высокоскоростные платы – это сложные устройства, где требуется планирование размещения компонентов и управление импедансом. Altium Designer предоставляет полный набор инструментов трассировки, работающих на основе правил проектирования, для реализации сквозной трассировки на платах DDR3 и DDR4. Функциональные возможности редактора плат Altium Designer упрощают создание топологии DDR3 или DDR4, обеспечивая целостность сигналов и простоту трассировки.

Чтобы узнать больше о сквозной трассировке для устройств DDR3 и DDR4, поговорите с экспертом Altium.