Signallaufzeitanpassung für High-Speed-Signale: Was Sie wissen müssen

Wenn wir zwei Signalanzeigen auf einem Oszilloskop betrachten, können wir sehen, wie falsch angepasste Längen/Timings zwischen Signalleiterbahnen nachgeschaltete Gates inkorrekt auslösen können. Problematischer wird die Situation, wenn wir uns die Übertragungszeit für ein Master-Taktsignal und die Hin- und Rücklaufzeit für gesendete/empfangene Daten in verschiedenen Computerschnittstellen ansehen. SDRAM löst dies elegant durch Platzieren eines Taktgebers im Slave-Gerät und Senden eines Taktsignals zusammen mit den abgerufenen Daten. Andere Schnittstellen (USB 3.0, SATA usw.) extrahieren das Taktsignal wiederum direkt aus den Daten.

Alle anderen Ansätze nutzen eine Signallaufzeitanpassung zwischen mehreren parallelen Verbindungen sowie Leiterbahnen in einem differentiellen Paar und mit Taktsignal, um zu gewährleisten, dass die Daten zur richtigen Zeit am richtigen Ort ankommen. Bei der Umsetzung jedes Längenabstimmungsschemas geht es um mehr als nur die einfache Länge. Vielmehr ist hierfür die Berücksichtigung von Signalverzögerungszeiten in verschiedenen Signalisierungs-/Schnittstellenstandards erforderlich. Hier erfahren Sie, was Sie über das Design für die Signallaufzeitanpassung und die Synchronisierung von Signalen wissen müssen.

Der Unterschied zwischen Signallaufzeitanpassung und Längenabstimmung

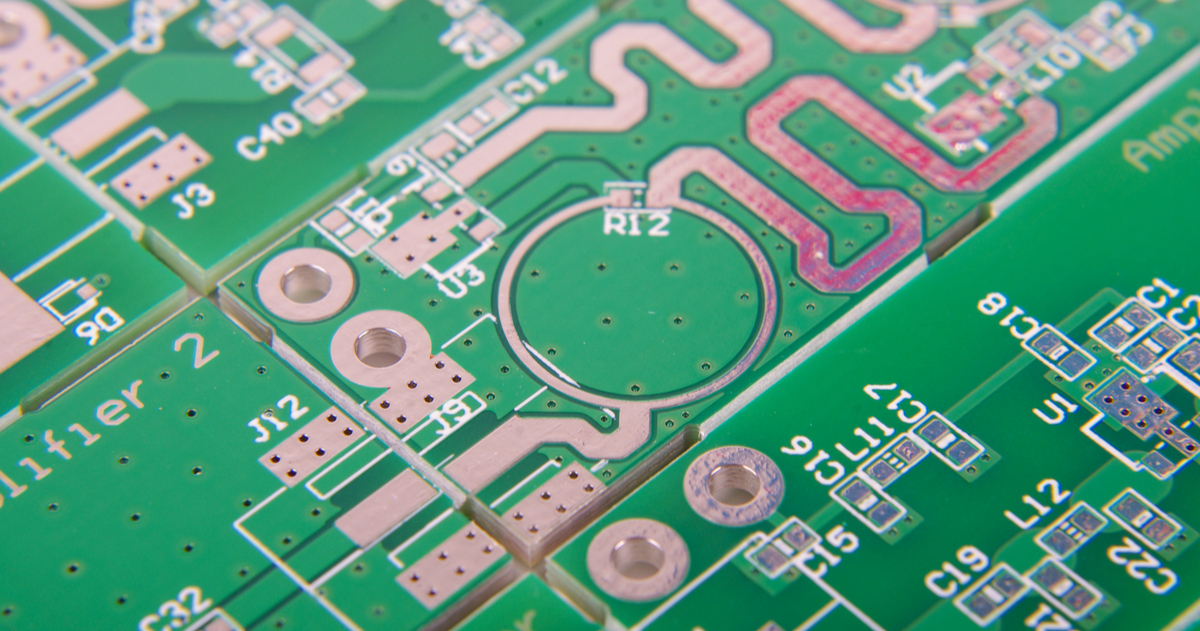

Die Längenabstimmung und die Signallaufzeitanpassung beruhen im Grunde auf der gleichen Idee; das Ziel ist es, die Längen der Signalleiterbahnen in einer angepassten Gruppe von Netzen auf den gleichen Längenwert einzustellen, um sicherzustellen, dass alle Signale innerhalb eines bestimmten Zeitunterschiedes ankommen. Wenn zwei Signalleiterbahnen innerhalb einer angepassten Gruppe nicht aufeinander angepasst sind, besteht der übliche Ansatz zur Synchronisierung der Signale darin, der kürzeren Signalleiterbahn durch Hinzufügen von gewissen Mäandern eine Verzögerung hinzuzufügen. Zu den typischen Mäander-Formen, die zur Verzögerung einer Leiterbahn verwendet werden, gehören Trombone-, Sawtooth- und Accordion-Muster.

Unabhängig davon, ob es darum geht, eine Signallaufzeitanpassung zwischen einem Taktsignal und mehreren Signalleitungen umzusetzen oder diese innerhalb eines differentiellen Paares oder zwischen mehreren differentiellen Paaren in Abwesenheit einer Taktleitung anzuwenden, man muss stets die spezifischen Timing-Toleranzen der Signale kennen. Bei Differentialpaar-Empfängern und Komponenten in SerDes-Kanälen sind die Signalanstiegszeit und die Signallaufzeit in einer Verbindung die begrenzenden Faktoren, die die zulässige Längenunterschiede zwischen den einzelnen Signalen bestimmen.

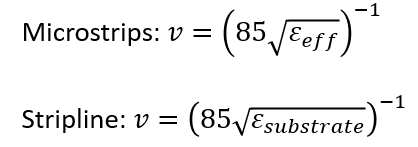

Für unterschiedliche Schnittstellen, die mit unterschiedlichen Datenraten und mit unterschiedlichen Signalisierungsstandards operieren, gelten unterschiedliche Toleranzen für Längen- oder Timing-Unterschiede. Diese Toleranzwerte basieren normalerweise auf der Annahme, dass Sie mit einem FR4-Substrat arbeiten, aber speziellere Designs auf Substraten mit einer anderen Dielektrizitätskonstante unterliegen anderen Toleranzen für Längenunterschiede. Bei der Planung von I/O-Kanälen auf Ihrer Leiterplatte sollten Sie diese zulässigen Toleranzen für Längenunterschiede für Ihre Leiterplatte nachschlagen und den zulässigen Längenunterschied in einen Timing-Unterschied umwandeln (siehe nachstehende Gleichung).

Arbeiten mit Timing-Unterschieden

Bei der Signallaufzeitanpassung geht es in erster Linie darum, mit einem Timing-Unterschied statt mit einem Längenunterschied zu arbeiten. Wenn Sie mit einer PCB-Design-Software arbeiten, die nur einen Längenunterschied berücksichtigt, dann müssen Sie den korrekten Längenunterschied für Ihr jeweiliges Substrat berechnen. Der Längenunterschied ist gleich dem Timing-Unterschied multipliziert mit der Signalgeschwindigkeit (Einheiten von in./ps) auf Ihrem jeweiligen Substrat:

In der Regel bedingt ein Substrat mit einer größeren Dielektrizitätskonstante eine geringere Signalgeschwindigkeit, wodurch sich der zulässige Längenunterschied zwischen zwei Signalen erhöht. In ähnlicher Weise führt die Übersteuerung von Standardkomponenten zu einer kürzeren Anstiegszeit (höhere Anstiegsgeschwindigkeit), was ebenfalls engere Beschränkungen für das Timing mit sich bringt. Um eine Annäherung erster Ordnung zu erreichen, sollte, wenn man die Anstiegszeit des Signals halbiert, auch die erlaubte Timing-Einschränkung halbiert werden.

Der zulässige Unterschied wird normalerweise in Form einer Toleranz für die Taktperiode und nicht für die Anstiegszeit definiert. Für eine gegebene Taktperiode ist der zulässige Längenunterschied umgekehrt proportional zur Signalgeschwindigkeit. Wenn Längenunterschiede mit einer angenommenen Dielektrizitätskonstante (z. B. FR4) angegeben werden, müssen Sie den Längenunterschied unter Verwendung der Signalgeschwindigkeit für Ihr spezielles Substratmaterial umrechnen.

Phasenfehlanpassung in differentiellen Paaren

Der Begriff "Phasenfehlanpassung" wird manchmal in einem Atemzug mit der Längenabstimmung und der Signallaufzeitanpassung genannt, aber bei der Arbeit mit differentiellen Paaren hat er eine wichtige Konsequenz. Beim Routing mit differentiellen Paaren kann es in bestimmten Fällen, z. B. wenn ein anderes Paar durch ungewöhnlich platzierte Vias geleitet werden muss, einen kurzen Bereich geben, in dem jedes Ende des Paares entkoppelt ist. Dieser Umstand kann zusätzlich zu einer unterschiedlichen Gesamtlänge des Paares auftreten, und zudem können auch mehrere Paare in einer abgestimmten Gruppe eine Längenabstimmung erfordern.

Die Phasenanpassung erfordert die Zugabe einiger kleiner Mengen Kupfer am nicht angepassten Ende, so dass die Längen der Leiterbahnen im entkoppelten Bereich angepasst sind. Dies ist ziemlich wichtig, um sicherzustellen, dass ein differentielles Paar Gleichtaktstörungen angemessen unterdrücken kann; jede Gleichtaktstörung, die im entkoppelten Teil induziert wird, sollte sich über die gleiche Entfernung ausbreiten, um sicherzustellen, dass sie in beiden Paaren angepasst bleibt, wenn sie den Empfänger erreicht.

Sie müssen die Leiterbahnlängen nicht manuell messen, wenn Sie die richtigen Längentoleranzen als Designregeln definieren.

Sobald die Phase in der entkoppelten Region angepasst ist, sollte überprüft werden, ob der Rest des differentiellen Paares längenangepasst ist, auch wenn die Länge im gesamten Paar eigentlich konsistent sein sollte, sofern dieses ursprünglich richtig geroutet wurde. Wenn dem differentiellen Paar ein längenangepasster Abschnitt hinzugefügt wird, um den Versatz zwischen den Paaren auszugleichen, sollte der längenangepasste Abschnitt symmetrisch über das gesamte differentielle Paar platziert werden. Es ist zu beachten, dass die Inter-Pair-Versatz-Beschränkungen in der Regel lockerer sind als die Intra-Pair-Versatz-Werte, um eine ausreichende Unterdrückung von Gleichtaktstörungen und die Signalextraktion zu gewährleisten.

Mehr über die Verzögerungsabstimmung: Der Pin-Verpackungs-Effekt

Sobald das Signal einen Pin/Pad auf einem bestimmten Bauteil erreicht hat, muss es noch durch den freiliegenden Leiter, entlang des Bonddrahts in das Innere des Gehäuses und in den Verpackungs-Die geleitet werden. Der freiliegende Leiter, das Pad/Pin und der Eingang zur internen Schaltung haben ein gewisses Maß an parasitärer Induktivität und Kapazität, und das Signal bewegt sich mit unterschiedlicher Geschwindigkeit entlang eines Bonddraht als entlang einer Signalleiterbahn. Die Bonddrähte weisen auch geringfügig unterschiedliche Geometrien auf, wodurch Signale auf verschiedenen Pins unterschiedlich stark verzögert werden.

Alle Gerätehersteller sollten in der Lage sein, Ihnen die Pin-Verzögerung für eine bestimmte Komponente mitzuteilen. Dieser Wert wird entweder als Verzögerung in Pikosekunden oder als Länge (normalerweise mm oder Mikrometer) angegeben. Sie sollten in der Lage sein, diesen Verzögerungswert aus der IBIS-6-Dokumentation für die jeweilige Komponente abzurufen. Diese Länge sollte bei der Durchführung jeder Art von Verzögerungs-/Längenabstimmung mit Signalen in einem differentiellen Paar oder bei mehreren synchronisierten differentiellen/einseitigen Signalen einbezogen werden.

Mit den leistungsstarken Tools für interaktives Routing- und Post-Layout-Analyse von Altium Designer® verfügen Sie über ein Komplettpaket, das auf einer einheitlichen regelbasierten Design-Engine aufbaut und Ihnen die Implementierung von Signallaufzeitanpassung für High-Speed-Signale und wichtige Signalintegritätssimulationen ermöglicht. Darüber hinaus verfügen Sie über einen kompletten Satz von Tools für die Erstellung von Schaltplänen, die Verwaltung von Komponenten und die Vorbereitung von Ergebnissen für Ihren Hersteller.

Jetzt können Sie eine kostenlose Testversion von Altium Designer herunterladen und mehr über die branchenweit besten Werkzeuge für das Layout, die Simulation und die Produktionsplanung erfahren. Sprechen Sie noch heute mit einem Experten von Altium, um weitere Informationen zu erhalten.