Leiterplattenentwurf für In-Circuit-Tests

In der Elektronikfertigung gibt es viele verschiedene Leiterplattentests mit spezifischen Zielen und Eigenschaften. Dieser Artikel enthält Richtlinien auf der Entwurfsebene (Schaltplan und Layout), die die Verwendung von Prüfadaptern für In-Circuit-Tests (ICT) ermöglichen, um die ordnungsgemäße Montage der Komponenten zu überprüfen. Mit diesen einfachen Prüfadaptern kann Ihre Leiterplatte im zusammengebauten Zustand getestet werden, wodurch fehlerhafte Leiterplatten identifiziert und aus dem Produktionsablauf entfernt werden können.

Die folgenden Checklisten können verwendet werden, wenn ein In-Circuit-Prüfadapter für Ihr Design entwickelt wird. Diese Richtlinien beziehen sich nicht auf Flying-Probe-Tester, Tools für die automatische optische Inspektion (AOI), Röntgen- oder Boundary-Scan-Technologie.

Checkliste zur Prüfbarkeit auf Schaltplanebene

Testpunkte können in Ihrem Schaltplan mit den CAD-Tools in Ihrem Schaltplaneditor ganz einfach erstellt werden. Sobald Sie Ihre Testpunkte erstellt haben, gibt es verschiedene Techniken, um In-Circuit-Tests zu ermöglichen und die Zuverlässigkeit des Tests sicherzustellen:

- IC-Steuerleitungen mit einzelnen Pull-up- oder Pull-down-Widerständen hoch oder niedrig binden

- Unbenutzte Eingänge mit einzelnen Pull-up- oder Pull-down-Widerständen hoch oder niedrig binden

- Einplanen einer Methode zur Deaktivierung von Taktsignalen (mit Hilfe von Jumpern, Tri-State-Puffern oder durch Aktivierung der Oszillatorleitung, falls verfügbar)

- Bereitstellung von Deaktivierungsmethoden für programmierbare logische Schaltungen (PLDs), anwendungsspezifische integrierte Schaltungen (ASICs) und andere benutzerdefinierte Bauelemente

- Bereitstellung von „Deaktivierungsmethoden“ für gebusste Bauelemente, Hochstrom-Bauelemente, Flash-RAMs, EEPROMs und D/A-Wandler

- Schaltungsanordnung zum Deaktivieren digitaler Rückkopplungsschleifen

- Bereitstellung eines Mittels zur Deaktivierung des platineneigenen PROM

- Trennung der Einschalt-Rücksetzschaltungen von anderen digitalen Schaltungen

Checkliste zur Prüfbarkeit auf PCB-Layout-Ebene

Hier sind einige Designrichtlinien für Testpunkte, die in Altium Designer auf der PCB-Seite implementiert werden können. Berücksichtigen Sie die folgenden Ideen so weit wie möglich, um die von Ihren Herstellern durchgeführten Tests zu unterstützen:

- Halten Sie Komponenten und Testpunkte mindestens 3,2 mm (.125) von den Platinenkanten entfernt (vorzugsweise 3,8 mm oder .150 in).

- Sorgen Sie für mindestens zwei unplattierte Werkzeuglöcher mit einem Durchmesser von 3,2 mm (0,125), vorzugsweise in gegenüberliegenden Ecken. Lassen Sie um diese Löcher herum einen ringförmigen Bereich von 3,2 mm frei und fügen Sie in diesen Bereich keine Komponenten und Testpunkte ein. Erwägen Sie die Verwendung eines "Keying"-Musters, so dass die Leiterplatten nicht rückwärts eingesetzt werden können.

- Ein doppelseitiger Prüfadapter ist teurer. Versuchen Sie daher, alle Testpunkte auf einer Seite der Leiterplatte zu platzieren, normalerweise auf der Unterseite oder auf der Seite mit der geringsten Schaltungskomplexität. Wenn die Oberseite der Platine für Sondenstellen verwendet werden muss, verwenden Sie die Oberseite nur für unkritische Netze. Belassen Sie die Testpunkte für Taktsignale, Steuerpins, Programmierpins, serielle Daten und Boundary Scan auf der Unterseite.

- Testpunktstellen können Durchgangsloch-Leitungen, dedizierte Pads oder Durchkontaktierungen mit kleinem Durchmesser sein, aber vermeiden Sie die Platzierung von Testpunkten auf oberflächenmontierten Flächen oder vergoldeten Edge-Fingern. Verwenden Sie für die Durchkontaktierungen keine größeren Durchmesser als für die Testpunktstellen. Die Größe der Durchkontaktierungen sollte 0,36 mm (.014) oder weniger betragen.

- Stellen Sie für jedes Netz mindestens ein Testpad zur Verfügung, um eine 100%ige Prüfbarkeit zu erreichen.

- Stellen Sie zwei Pads auf Netzen bereit, die an kritische niederohmige Bauelemente gebunden sind (Vier-Draht-Kelvin-Test).

- Stellen Sie 2-10 Sondenstellen für die primäre Stromversorgung und mindestens zwei Testpunkte für jedes isolierte Stromversorgungs-/Erdungsnetz bereit.

- Sondenstellen mit einem Pad-Durchmesser von 1,0 mm (.040) werden bevorzugt, 0,9 mm (.035) sind akzeptabel, 0,8 mm (.031) können verwendet werden, wenn Werkzeuglöcher für die Ausrichtung zur Verfügung stehen, aber kleinere Durchmesser verringern die Kontaktwiederholbarkeit.

- Versuchen Sie, die Sondenstellen mit mindestens 2,5 mm (.100) Abstand, von Mitte zu Mitte, zu platzieren. In Wirklichkeit werden 0,9 mm (.035) Pads im Abstand von 1,8 mm (.070) von vielen als Standard angesehen. Engere Abstände sind möglich, erfordern jedoch die Verwendung dünnerer, weniger zuverlässiger und teurerer Sonden.

- Die Testpunkte sollten gleichmäßig über die Oberfläche der Leiterplatte verteilt sein. Hohe Spannungen in überlasteten Bereichen können zum Verziehen der Leiterplatten führen.

- Lassen Sie hohe Komponenten auf der Seite, die nicht geprüft wird. Die Leiterplatte muss an Stellen ausgeschnitten werden, an denen die Komponenten auf der getesteten Seite über 6,4 mm (.255) hoch sind. Für diese müssen die Testpunkte mindestens 5,0 mm (.200) entfernt gehalten werden.

- Bei Komponenten, die höher als 2,6 mm (.100) sind, ist ein Abstand von mindestens 2,0 mm (.080) von Kante zu Kante einzuhalten. Bei allen anderen Komponenten müssen die Testpunkte mindestens 1,0 mm (.040) vom Komponentenkörper entfernt sein, von Kante zu Kante.

- Wenn Komponenten-Durchgangslöcher für die Sondenstellen verwendet werden, stellen Sie sicher, dass die Leitungen robust genug für Druckkräfte sind (seien Sie vorsichtig bei der Verwendung von LEDs oder einigen Transformatorentypen). Stellen Sie außerdem sicher, dass PTH-Leitungen an allen Versionen der Baugruppe vorhanden sind (nicht unbestückt).

- Wenn das Design panelisiert ist, versuchen Sie, zusätzlich zu den Werkzeuglöchern in Schienen mindestens ein Werkzeugloch auf jeder Platine vorzusehen.

Konfigurieren von Testpunkten für In-Circuit-Tests

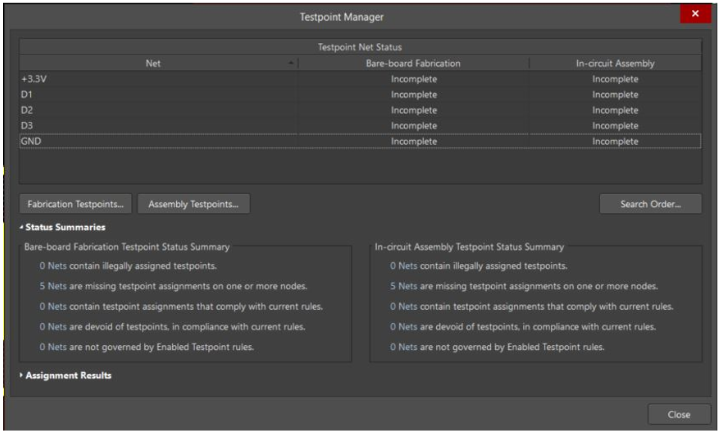

Altium Designer® bietet einen Testpoint Manager, der Sie bei der Analyse Ihres Designs auf Prüfbarkeit unterstützt.

Gehen Sie hierfür zum Hauptmenü > Tools > Testpoint Manager:

Revision von Designs mit vorhandenen ICT-Prüfadaptern

Prüfadapter sind sehr teuer, aber es ist oft möglich, einen bestehenden Adapter für eine Revision zu modifizieren, statt einen neuen zu entwickeln. Wenn es möglich ist, einen vorhandenen Adapter zu verwenden, wird es einfacher, schneller und kostengünstiger sein, wenn Sie den folgenden Richtlinien folgen:

- Bewegen Sie die Werkzeuglöcher nicht.

- Bewegen Sie keine Testpunkte, es sei denn, dies ist absolut notwendig.

- Setzen Sie einen neuen Testpunkt nicht innerhalb von 0,100" von einem vorhandenen Testpunkt (oder von einem Testpunkt, der entfernt wird).

- Benennen Sie keine vorhandenen Komponenten um.

- Benennen Sie keine neuen Komponenten mit dem gleichen Namen wie Komponenten, die entfernt wurden.

- Wenn sich eine Verbindung in einem Netz geändert hat, benennen Sie das Netz um.

- Wenn sich ein Netz in zwei oder mehr Netze aufteilt, verwenden Sie nicht den alten Netznamen wieder, sondern erstellen Sie neue Netznamen.

- Selbst wenn der ursprüngliche Testpunktdurchmesser kleiner war, versuchen Sie, den Durchmesser der neuen Testpunkte auf bis zu 0,040" zu vergrößern, um einen zuverlässigen Kontakt zu gewährleisten. (Wenn Prüfadapter-Hersteller Löcher für Sondenbuchsen in einen vorhandenen Adapter nachbohren, sind diese möglicherweise nicht mehr so genau wie bei der ursprünglichen Herstellung).

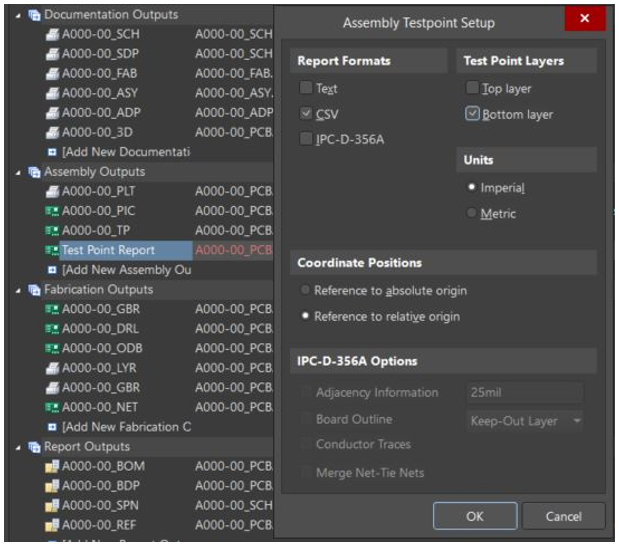

Erstellung eines Testpunktberichts für die Fertigung

Das Altium Designer System kann den Testpunktbericht exportieren, und Sie können dies als Teil Ihrer OutJob-Konfiguration automatisieren:

Zusammenfassung

Mit den Ideen in diesem Artikel sind Ihre In-Circuit-Testprogramme einfacher zu implementieren, die Fehlerwahrscheinlichkeit wird reduziert und Anpassungen für Revisionen werden kostengünstiger und zuverlässiger.

HAFTUNGSAUSSCHLUSS: Die hier gegebenen Ratschläge sollten lediglich als Leitfaden verstanden werden, um Ihnen den Einstieg zu erleichtern. Die Elektronikindustrie bewegt sich schnell, und Normen ändern sich ständig. Wenn irgendetwas, was im obigen Artikel erwähnt wird, Ihrem eigenen Designprozess widerspricht, sollten Sie sich mit Ihren Fertigungspartnern beraten und Anpassungen (falls vorhanden) vornehmen, um Ihrem In-Circuit-Testprozess zu entsprechen.

Für weitere Informationen

Hier ist die von der Surface Mount Technology Association veröffentlichte Prüfbarkeitsnorm:

SMTA-TP-101 TESTABILITY GUIDELINES

Altium-Dokumentation

Weitere Informationen über das Testen in der Fertigung finden Sie in diesem Altium Blog-Artikel von Kella Knack:

Möchten Sie mehr darüber erfahren, wie Altium Ihnen bei Ihrem nächsten Leiterplatten-Design helfen kann? Sprechen Sie mit einem Experten von Altium.